## Tutorial on Agile Research Test Chips Introduction

Paul Whatmough Marco Donato Glenn G. Ko Sae-Kyu Lee David Brooks Gu-Yeon Wei

School of Engineering and Applied Sciences

Harvard University

#### **CHIPKIT Materials**

#### **IEEE Micro paper**

- https://ieeexplore.ieee.org/document/9096507

- https://arxiv.org/abs/2001.04504

#### Open source Github project

https://github.com/whatmough/CHIPKIT

## Who are we?

Paul Whatmough Arm Research Harvard University

Marco Donato Harvard University

Glenn G. Ko Harvard University

Sae-Kyu Lee IBM Research

David Brooks Harvard University

Gu-Yeon Wei Harvard University

## Why build test chips in research?

#### Circuits research

Measured test chip required for tier-1 publication

#### Architecture research

- Understand the whole stack, soup to nuts

- Know you are solving a real problem

- Add real impact to your work; not just another academic paper

#### All models are wrong, some are useful

- Many things are hard to simulate convincingly

- Data to build models to design better circuits

#### Training for industry

- Build a deep understanding of real computers

- Problem solving, teamwork, time management

- Extremely valuable depth of experience

#### CHIPKIT tutorial

- Many groups routinely tape out test chips in research environments

- The first few are typically very challenging, climbing a steep learning curve by trial and error

- Once you know how to do it, it's easy heavily reuse the last chip!

- Currently a huge amount of activity around open hardware

- Open source IP from universities

- Commercial IP available to academia

- Never been a better time to get into research test chips!

- But there is still a knowledge gap in terms of turn this into working test chips

## Who is this tutorial for?

- Those looking to:

- Do their first tape outs

- Start develop more sophisticated test chips

- Reduce the time to develop and maintain their SoCs and custom IPs

## Goals of the tutorial

- Provide a source of more fundamental material on research tape outs

- Provide high-level overview of the front-end design and validation of

- A simple M-Class (Microcontroller) SoC

- A simple A-Class (Apps Processor) SoC

- A simple custom IP block

- An overview of the physical design flow

- An overview of bring up and testing

- Bring together researchers with a shared interest in research test chips

- Andrew Kahng (UCSD) Open source implementation tools

- Christopher Batten (Cornell) PyMTL3

- Adrian Sampson (Cornell) Predictable accelerator design

- Thierry Tambe (Harvard) High-level synthesis

- Shuojin Hang (Arm) Arm academic enablement

# Tutorial on Agile Research Test Chips M-Class SoC Development

Paul Whatmough Marco Donato Glenn G. Ko Sae-Kyu Lee David Brooks Gu-Yeon Wei

School of Engineering and Applied Sciences

Harvard University

#### **CHIPKIT Materials**

#### **IEEE Micro paper**

- https://ieeexplore.ieee.org/document/9096507

- https://arxiv.org/abs/2001.04504

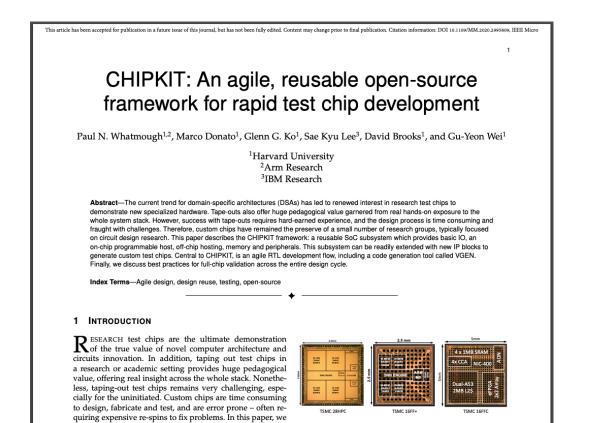

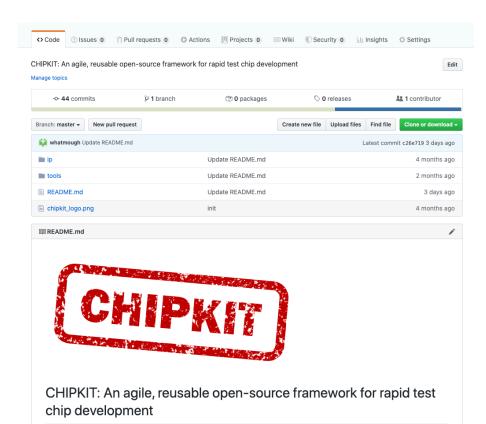

## CHIPKIT: An agile, reusable open-source framework for rapid test chip development

Paul N. Whatmough<sup>1,2</sup>, Marco Donato<sup>1</sup>, Glenn G. Ko<sup>1</sup>, David Brooks<sup>1</sup>, and Gu-Yeon Wei<sup>1</sup>

<sup>1</sup>Harvard University <sup>2</sup>Arm Research

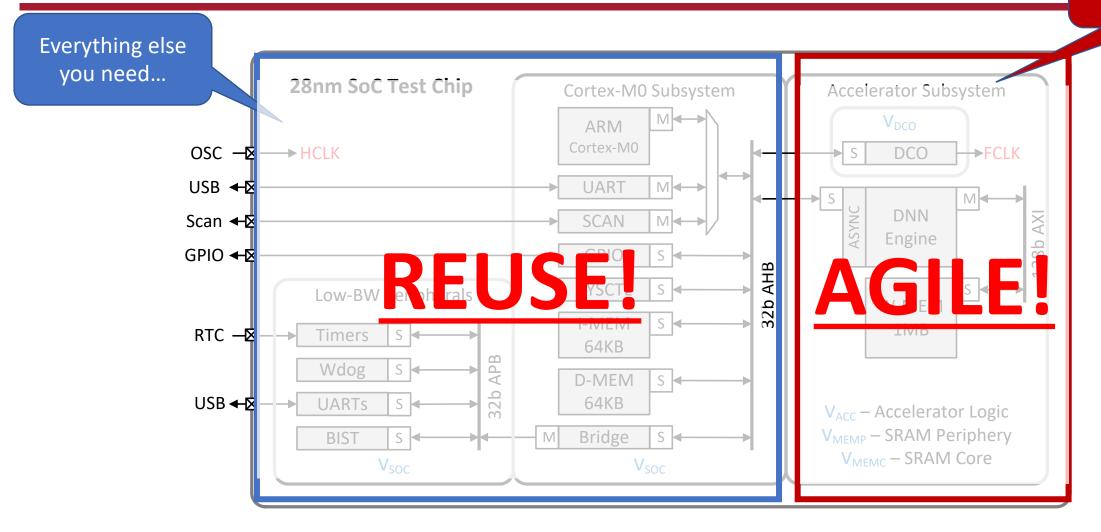

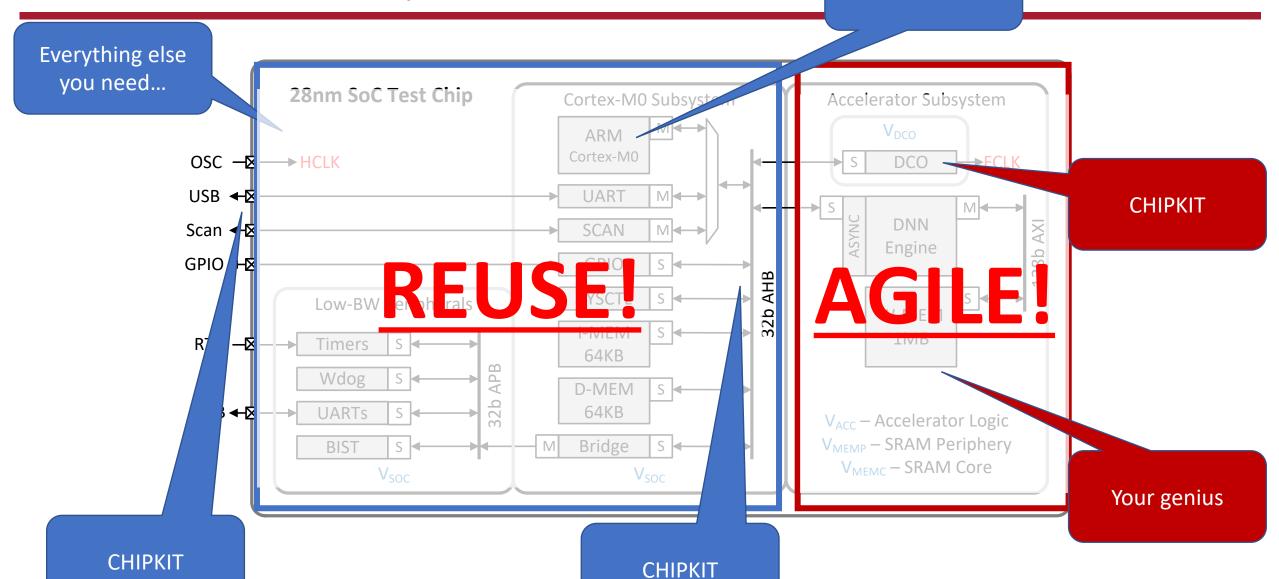

Abstract—The current trend for domain-specific architectures (DSAs) has led to renewed interest in research test chips to demonstrate new specialized hardware. Tape-outs also ofter huge pedagogical value garnered from real hands-on exposure to the whole system stack. However, successful tape-outs demand hard-earned experience, and the design process is time consuming and fraught with challenges. Therefore, custom chips have remained the preserve of a small number of research groups, typically focused on circuit design research. This paper describes the CHIPMT framework. We describe a reusable SOC subsystem which provides basic IO, an on-chip programmable host, memory and peripherals. This subsystem can be readily extended with new IP blocks to generate oustom test chips. We also present an agile RTL development flow, including a code generation tool called VGEN. Finally, we outline best practices for full-chip validation across the entire design cycle.

Index Terms-Agile design, design reuse, testing, open-source

#### 1 Introduction

3

D ESEARCH test chips are the ultimate demonstration of In the true value of novel computer architecture innovations. In addition, taping out test chips in a research or academic setting provides huge pedagogical value, offering real insight across the whole stack. Nonetheless, despite all the upsides, taping-out test chips remains very challenging, especially for the uninitiated. Custom chips are time consuming to design, fabricate and test, and often error prone potentially requiring expensive re-spins to fix problems. In this paper, we explore two key themes of agile and reusable design, to help reduce the barrier to entry for chip tape-outs. Emphasizing reuse greatly reduces development cost and at the same time minimizes the opportunity for silicon bugs and allows the designer to focus on differentiating features. While agile design seeks to follow a methodology where changes can be readily implemented late into the design cycle, without significant disruption or risk.

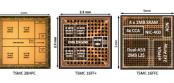

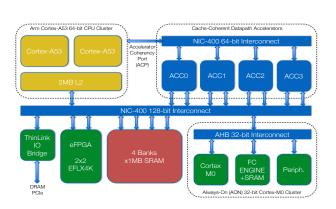

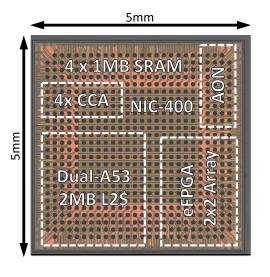

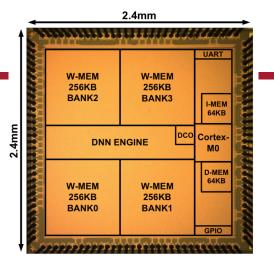

Fig. 1. Three recent chips [1], [2], [3] built using the CHPIKIT framework

[2], through to large multi-accelerator SoCs with Arm Cortex-A multi-core CPU clusters [3]. However, they all share the same basic framework, with the same SoC subsystem for system bring up, communication and control. Following this framework has allowed new tape-outs to be developed with very low-risk and high success rate. To be In

#### Open source Github project

https://github.com/whatmough/CHIPKIT

## Q&A session

CHIPKIT Tutorial Sun. May 31, 2020

## Different complexities of test chips

Analog and Test Structures

M-Class SoCs

A-Class SoCs

## Outline

- Opportunities for agile and reusable design

- SoC Bus Fabrics

- M-Class Off-Chip Interfaces

- On-Chip Memories: SRAMs and Control and Status Regs (CSRs)

- Clocks, Resets and Power Domains

- Summary

- Recommended Reading

# Opportunities for agile and reusable design

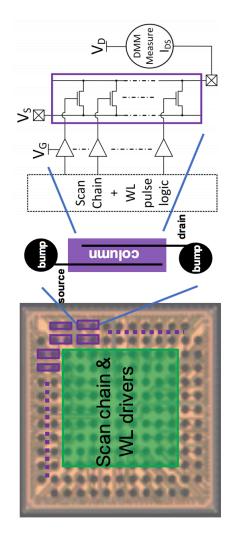

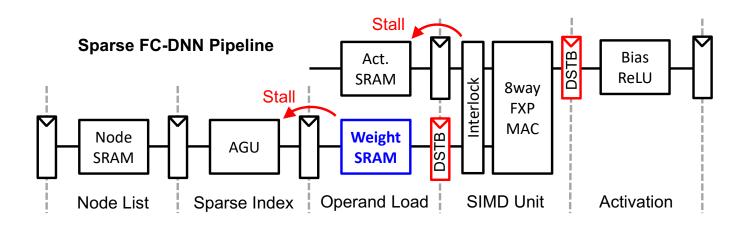

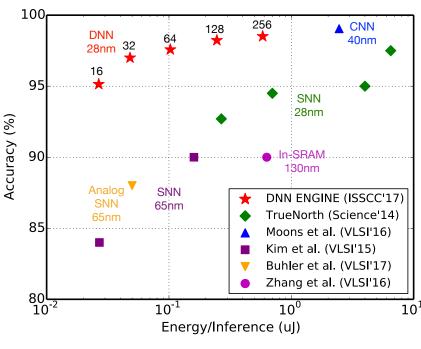

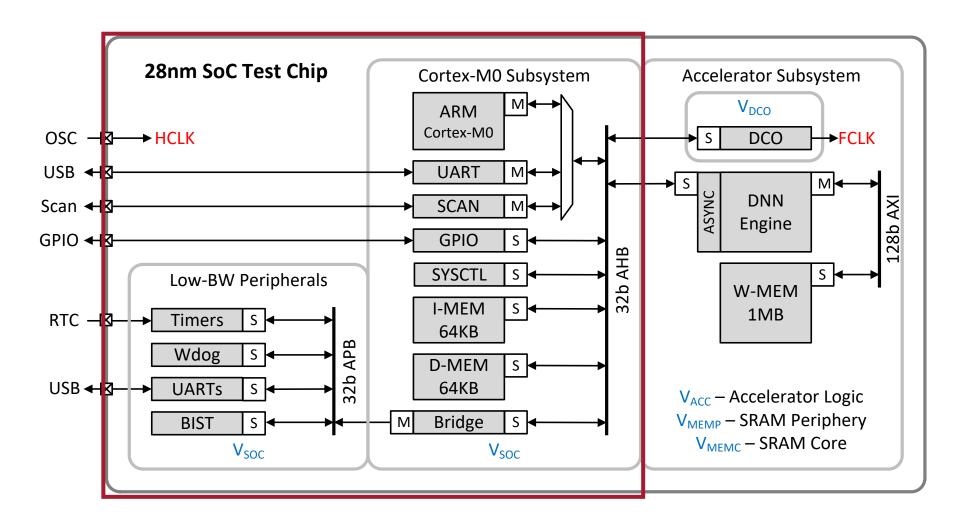

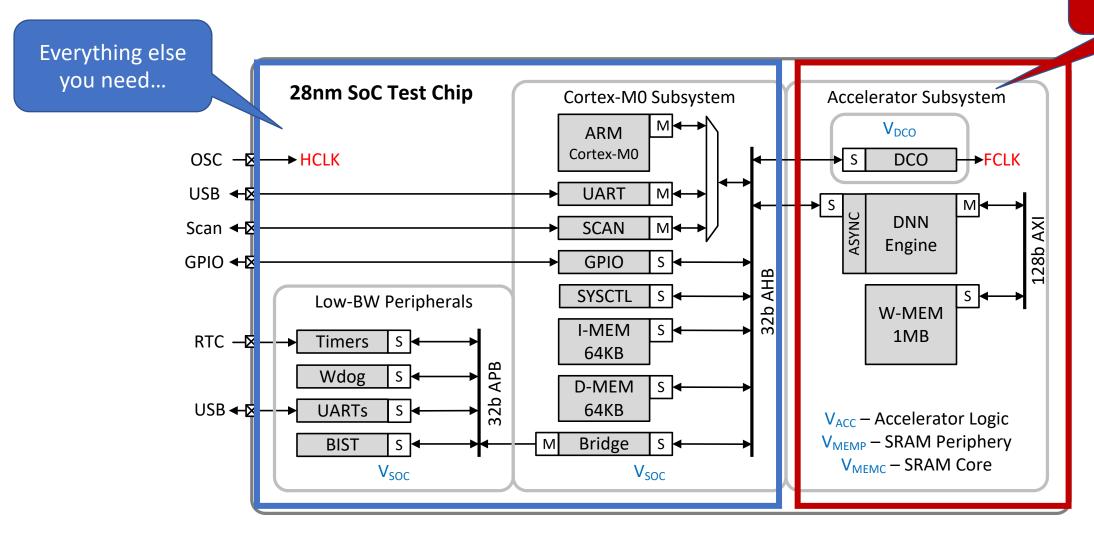

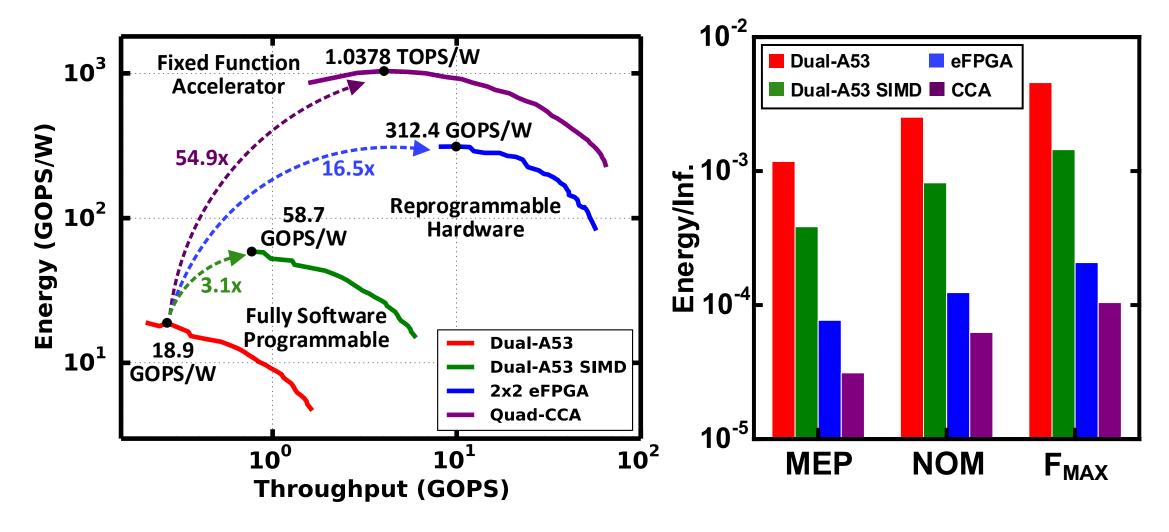

## SM2 – 28nm DNN ENGINE Accelerator

- Programmable DNN Classifier for IoT

- Parallelism/reuse 8-way SIMD, 10X data reuse @ 128b/cycle BW

- Small data-types 8-bit weights, –30% energy

- Sparse activation data +4X throughput and -4X energy

- Algorithmic resilience +50% throughput or -30% energy

[Whatmough et al., ISSCC '17, JSSC '18, Hot Chips'17]

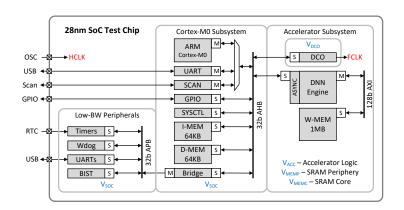

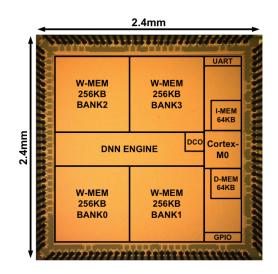

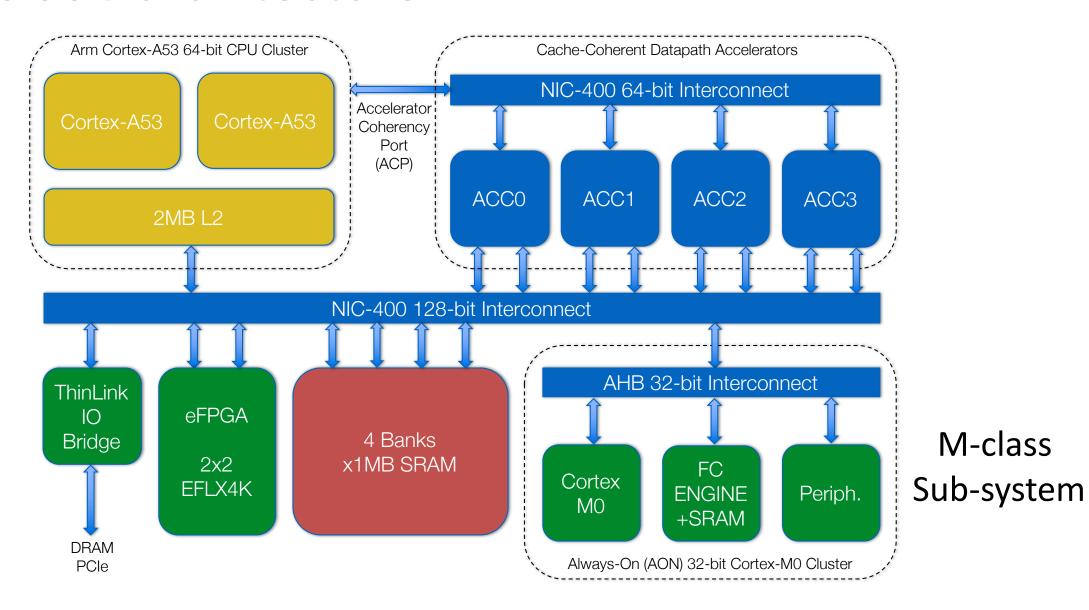

## M-Class Test Chip Architecture

## M-Class Test Chip Architecture

Arm DesignStart

## SoC Bus Fabrics

## On-Chip Bus Protocols

- Stick to industry standard bus protocols

- Exploit well documented public standards

- Reuse protocol checkers and other verification IP

- Compatible with a broad IP ecosystem

- Avoid temptation to "modify"

- AMBA open standards

- APB low-performance, low area

- AHB general purpose

- AXI high-performance

- Many others...

- WISHBONE (OpenCores)

- Open Core Protocol (OCP)

- CoreConnect (IBM)

- TileLink (RISC-V)

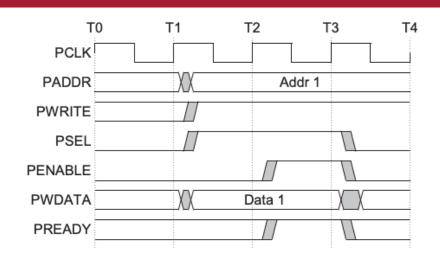

## Advanced Peripheral Bus (APB)

- Simple bus for connecting master to multiple slaves

- Low hardware cost due to simple control and small number of signals

- Ideal for low-bandwidth peripherals and control signaling

- Data width up to 32 bits

- Non-pipelined, slave can insert wait cycles

- Every transfer takes a minimum of two cycles

- Synthesis friendly

- Simple single-edge clocked timing, no tri-state buses

- One data bus for read and another for write

- APB is a reasonable option for very low-bandwidth peripherals and IO

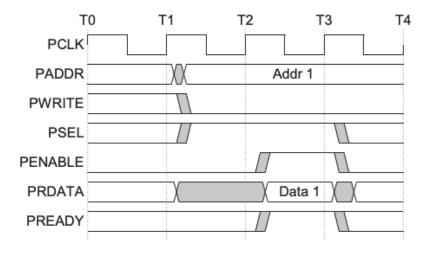

## APB — Basic Transactions

- Setup phase (T1)

- Transfer starts with address PADDR, write data PWDATA, write signal PWRITE, and select signal PSEL, being registered at the rising edge of PCLK

- Access phase (T2),

- Enable signal PENABLE, and ready signal PREADY, are registered at the rising edge of PCLK

- When asserted, PENABLE indicates the start of the Access phase of the transfer.

- When asserted, PREADY indicates that the slave can complete the transfer at the next rising edge of PCLK.

- The address PADDR, write data PWDATA, and control signals all remain valid until the transfer completes at the end of the Access phase (T3).

Figure 3-1 Write transfer with no wait states

Figure 3-4 Read transfer with no wait states

## Advanced High-performance Bus (AHB)

- Similar to APB, this is a shared bus protocol for multiple masters and slaves, but higher bandwidth is possible through burst data transfers.

- AHB-lite protocol is a simplified version of AHB, designed for a singlemaster system

- Large bus-widths up to 1024 bits

- We recommend to use AHB-lite widely where performance is not critical

- Simple to implement and debug

- Good eco-system support

- Very low hardware cost

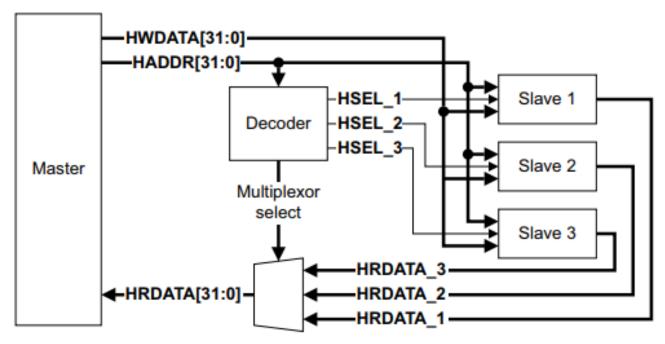

#### **AHB**

- A typical AHB transaction consists of an address phase and a subsequent data phase, which are pipelined

- A simple address decoder generates slave select signals and controls the muxing of read data back to the master in the data phase

Figure 1-1 AHB-Lite block diagram

#### **AHB**

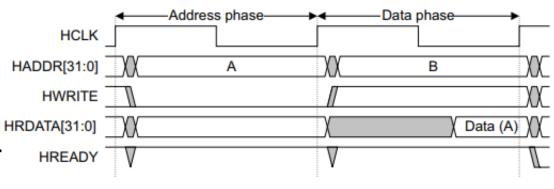

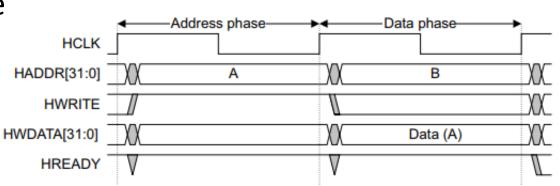

- Every transfer consists of:

- Address phase one address and control cycle

- Data phase one or more cycles for the data

- The address phase of any transfer occurs during the data phase of the previous transfer (i.e. they are pipelined)

- A slave cannot request that the address phase is extended and therefore all slaves must be capable of sampling the address in one cycle

- However, a slave can request that the master extends the data phase using HREADY

- This signal, when LOW, extends the transfer to give the slave extra time

Figure 3-1 Read transfer

Figure 3-2 Write transfer

## Advanced eXtensible Interface (AXI)

- The Advanced Extensible interface (AXI) is very common for higher performance interconnects

- More flexible

- Scalable point to point interconnect, easy to pipeline and close timing on big complex SoCs

- More features

- Supports multiple outstanding data transfers, burst data transfers, coherency (with extensions) etc.

- Also... more variants

- AXI-stream protocol is effectively the basis of the AXI protocol, for streaming data from a master to a slave using a simple valid/ready handshake

- AXI-lite protocol is a simplified version of AXI, removing burst data transfers

- AXI Coherency Extensions (ACE and ACE-Lite), extend AXI with additional signaling that enables system wide coherency or IO coherency

- We'll come back to AXI in the A-class SoC section

- AXI-lite can be useful for simpler test-chips, but AHB is even simpler

## On-Chip Interconnect IP

- Choose bus interfaces based on required features and performance

- Strong eco-system around AMBA open standards, but there are other credible choices too ©

- RTL interconnect implementations need to be robust

- Critical to operation of SoC, must work 100% verification is essential

- Should be flexible and easy/robust to make changes as the tape out project evolves

- Typically need multiple busses

- Often partition buses (even on simple chips) based on usage and traffic types and volumes

- Helps with throughput, as well as design and verification

- Use bridges to inter-connect buses of the same or different or protocols

- Use standard / verified bus interfaces and RTL implementations where possible

- Time to quality greatly reduced

- Minimize the chance of critical bugs that could lead to a dead block or even a broken SoC

- Spend time on the differentiating part

- Reuse protocol checkers and compatibility with the whole SoC eco-system

- Simple single-layer AHB-lite Interconnect IP

- Uses bundled SystemVerilog Interfaces to vastly reduce typing

- Configures address decoder based on a single memory map header file

- Easy to update as the tape out project evolves, by editing only a single file

- Automatic default slave in the decoder to catch accesses to unused regions

• SystemVerilog interfaces bundle signals, parameters, assertions, ...

```

AHB Slave

nterface ahb_slave_intf

parameter DW=32,

parameter AW=32,

parameter STUB=0

nput logic HCLK,

// for assertions in interface

nput logic HRESETn

/ Global signals

// Slave Select

// Address, Control & Write Data

ogic HREADY;

ogic [AW-1:0] HADDR;

ogic [1:0] HTRANS;

//logic HPROT;

ogic HWRITE;

ogic [DW-1:0] HWDATA;

// Transfer Response & Read Data

ogic [DW-1:0] HRDATA;

ogic HRESP;

// Source is slave side

odport source (input HSEL, HADDR, HTRANS, HWRITE, HSIZE, HWDATA, HREADY, output HREADYOUT, HRDATA, HRESP);

// Sink is bus matrix side

odport sink (output HSEL, HADDR, HTRANS, HWRITE, HSIZE, HWDATA, HREADY, input HREADYOUT, HRDATA, HRESP);

// Assertions on outgoing slave signals

ERROR_slave_emitted_undefined_HREADY :

SSERT_CLK(HCLK, HRESETn, !$isunknown(HREADY));

ERROR_slave_emitted_undefined_HRESP :

ASSERT_CLK(HCLK, HRESETn, !$isunknown(HRESP));

ndinterface

```

```

AHB master

interface ahb_master_intf

/import sm2_defs_pkg::*;

parameter DW=32,

arameter AW=32,

parameter STUB=0

input logic HCLK,

// for assertions in interface

nput logic HRESETn

Global signals

Address, Control & Write Data

ogic HREADY;

ogic [AW-1:0] HADDR;

ogic [1:0] HTRANS;

/logic [2:0] HBURST;

/logic [3:0] HPROT;

/logic HMASTLOCK;

ogic [2:0] HSIZE;

ogic [DW-1:0] HWDATA;

/ Transfer Response & Read Data

logic [DW-1:0] HRDATA;

logic HRESP;

/ Source is slave side

dport source (input HREADY, HRESP, HRDATA, output HTRANS, HWRITE, HWDATA, HSIZE, HADDR);

Sink is bus matrix side

odport sink (output HREADY, HRESP, HRDATA, input HTRANS, HWRITE, HWDATA, HSIZE, HADDR);

/ Assertions on outgoing Master signals

ERROR_master_emitted_undefined_signals :

ASSERT_CLK(HCLK,HRESETn,!$isunknown(

TRANS[1:0], HWRITE, HSIZE, HADDR[31:0], HWDATA[31:0]}

endinterface

```

- Wrap legacy IP to bundle bus interface

- This example shows an Arm Cortex-M0

```

input logic HCLK, HRESETn,

ahb_master_intf.source M,

input logic NMI,

input logic [31:0] IRQ,

output logic

input logic

output logic

LOCKUPREQ

output logic

nput logic [25:0]

STCALIB,

utput logic

CMO does not use HMASTLOCK, HPROT and HBURST.

Cortex-M0 processor instantiation

ogic txev_pulse, rxev_pulse;

ORTEXMODS u_cortexm0 (

// CLOCK AND RESETS -

.HRESETn

(HRESETn),

// AHB-LITE MASTER PORT ---

(M.HADDR[31:0]), // AHB transaction address

(), // Not using // AHB burst: tied to single

.HMASTLOCK

(), // Not using // AHB locked transfer (always zero)

(), // Not using // AHB protection: priv; data or inst

(M.HSIZE[2:0]),

(M.HTRANS[1:0]),

// AHB size: byte, half-word or word

// AHB transfer: non-sequential only

(M.HWDATA[31:0]),

// AHB write-data

.HWRITE

(M.HWRITE),

// AHB write control

(M.HRDATA[31:0]),

// AHB read-data

(M.HREADY),

// AHB stall signal

(M.HRESP),

// AHB error response

MISCELLANEOUS

.NMI

// Non-maskable interrupt input

// Interrupt request inputs

(txev_pulse),

// Event output (SEV executed)

(rxev_pulse),

// Event input

(LOCKUPREQ),

(SYSRESETREQ),

(STCALIB[25:0]),

// Core is locked-up

// System reset request

.STCALIB

// SysTick calibration register value

// SysTick SCLK clock enable

.SLEEPING

(SLEEPING)

// Core and NVIC sleeping

```

Decoder memory map controlled by a single SystemVerilog package

```

package cm0_memmap_pkg;

// _START is first valid address (inclusive),

// _END address is inclusive!

localparam logic [31:0] S0_ADDR_START

= 32'h0000_0000; // SRAM program mem

= 32'h0000_FFFF;

localparam logic [31:0] S0_ADDR_END

// 64KB

localparam logic [31:0] S1_ADDR_START

= 32'h0400_0000;

// SRAM data mem

localparam logic [31:0] S1_ADDR_END

// 64 KB

// APB subsystem peripherals

localparam logic [31:0] S2_ADDR_START

localparam logic [31:0] S2_ADDR_END

= 32'h1003_FFFF;

// 64KB

localparam logic [31:0] S3_ADDR_START

= 32'h1001_0000;

// GPI00

localparam logic [31:0] S3_ADDR_END

// 64KB

localparam logic [31:0] S4_ADDR_START

= 32'h1002_0000;

// GPI01

localparam logic [31:0] S4_ADDR_END

// 64KB

localparam logic [31:0] S5_ADDR_START

// SYSCTL

localparam logic [31:0] S5_ADDR_END

// 64KB

= 32'h1800_0000;

localparam logic [31:0] S6_ADDR_START

// ACC0

localparam logic [31:0] S6_ADDR_END

// 16MB - 24b interal address width

localparam logic [31:0] S7_ADDR_START

// CRG

// 64KB

localparam logic [31:0] S7_ADDR_END

// NICTOP - lower region

localparam logic [31:0] S8_ADDR_START

localparam logic [31:0] S8_ADDR_END

= 32'h0FFF_FFFF;

localparam logic [31:0] S9_ADDR_START

= 32'h2000_0000; // NICTOP - upper region

localparam logic [31:0] S9_ADDR_END

= 32'hFFFF_FFFF;

// AHB timeout for assertions

localparam integer SM2_AHB_SLAVE_TIMEOUT = 999;

endpackage

```

## M-Class Off-Chip Interfaces

## Basic IO

- System clock

- From PCB crystal

- Power-on Reset (PoR)

- On a test chip, typically driven from a PoR circuit on the PCB

- Test pins, such as scan test IO

- Real-time clock

- CPU debug interfaces

- General-purpose IO

- Software programmable, very useful, e.g. for working around problems or testing purposes

## **UART Slave Peripherals**

- Important for software, typically retarget printf() to UARTs

- Plus use in RTL simulation to control simulation termination

- Speed typically not that important for simple terminal communication

- But, beware UARTs limiting RTL simulation runtime

- Include a very high baud rate option just for RTL sims to avoid this problem

- Use a UART to USB transceiver on the PCB

- This allows a simple USB cable to a laptop, which can then communicate with the test chip interactively using a terminal emulator or in a python script

- Can be useful to have multiple UART slaves, especially in multi-core systems which are more difficult to bring-up and debug

## CHIPKIT UART Master Peripheral IP

- For test chips, integrating higher-performance IO is challenging and risky

- For example, HW and SW integration for on-chip USB is non-trivial

- In practice, many research chips use simple IO for programming and moving data

- Simple IP for off-chip hosting over UART

- Very simple and robust bus master interface onto the SoC

- Perform on-chip bus transactions from laptop terminal over USB

- No CPU overhead, very simple to integrate HW and SW

- Provides a simple interactive text interface in the terminal, no SW required

- Write transaction -> w(rite) 0x0700000F 0xDEADBEEF

- Read transaction -> r(ead) 0x0700000F (-> 0xDEADBEEF)

- Python tool for loading data and scripting up tests

- Chip LOad Tool (CLOT)

## CHIPKIT VGEN IO Script

- VGEN script for generating and managing IO throughout the project

- Uses Python VGEN infrastructure for generators (we'll come back to this)

- CSV database of IO signals

- Entered manually or automatically generated from the top level SoC netlist

- Updated automatically as things are added/removed

- Generates/updates lots of useful "code" in seconds

- Pad ring RTL, pad ring instance, testbench interface, EDA scripts etc

- Very easily extensible

## CHIPKIT VGEN IO Script

| M5 Ţ         | $\times$ $\checkmark$ $f_x$ |      |      |                                             |   |   |   |

|--------------|-----------------------------|------|------|---------------------------------------------|---|---|---|

| A            | В                           | С    | D    | E                                           | F | G | н |

| 1 name       | direction                   | side | bump | description                                 |   |   |   |

| 2            |                             |      |      |                                             |   |   |   |

| 3 # Clocks   |                             |      |      |                                             |   |   |   |

| 4 HCLK       | input                       | 3    | Z9   | This is a clock (example description field) |   |   |   |

| 5 EXTCLK0    | input                       | 3    | Z12  |                                             |   |   |   |

| 6 EXTCLK1    | input                       | 3    | Z11  |                                             |   |   |   |

| 7            |                             |      |      |                                             |   |   |   |

| 8 TLXFWD_CL  | output                      | 2    | 11   |                                             |   |   |   |

| 9 TLXREV_CLK | input                       | 1    | A18  |                                             |   |   |   |

| LO           |                             |      |      |                                             |   |   |   |

| 1 # Resets   |                             |      |      |                                             |   |   |   |

| 2 PORESETn   | input                       | 3    | Y10  |                                             |   |   |   |

| B TIVEWD BS  | output                      | 2    | 12   |                                             |   |   |   |

```

default_nettype none

module

// VGEN: MODULE NAME

TOP_PADS

// VGEN: MODULE DECLARATION

input

wire

PAD_HCLK,

wire

PAD_EXTCLK0,

input

PAD_EXTCLK1,

input

wire

output wire

PAD_TLXFWD_CLK,

wire

PAD_TLXREV_CLK,

input

PAD PORESETn

```

```

// Module instantiation.

TOP_PADS uTOP_PADS (

.PAD_HCLK,

.PAD_EXTCLK0,

.PAD_EXTCLK1,

.PAD_TLXFWD_CLK,

.PAD_TLXREV_CLK,

.PAD_PAD_PORESETn.

```

## Diagnostic (DIAG) Signal Mux

- Sometimes with test chips, things don't go as planned ©

- Debugging problems inside a fabricated chip can be very challenging

- In the worst case, it can really help to have visibility into the system

- UART bus master allows access to the on-chip bus to poke registers and RAMs

- But what if there's a more subtle problem?

- It helps a lot to have visibility of key signals on-chip, but can't pin out everything

- Clocks, resets, power rails, power gate enables, interrupts etc

- Diagnostic (DIAG) signal mux allows more signals to be pinned out by using a big mux to select a signal to drive a pin from a larger group of options

- Having two DIAG pins allows interaction of multiple things, e.g. check clock and reset at the same time

- Easily generated automatically using a VGEN script

# On-Chip Memories: SRAMs and Control and Status Regs (CSRs)

### Scratchpad SRAMs

- SRAMs need to be wrapped with a bus interface

- This can range from very simple to very complex

- For M-Class systems, typically a simple AHB interface

- Easy to overlook verification things like memory-mapped SRAMs

- Common mistakes include accidental truncation of address bits somewhere

- Be sure to test across the full address range, not just the first few words

## CHIPKIT Scratchpad SRAMs

AHB\_MEM.sv

## Control and Status Registers (CSRs)

- CSRs are very common in memory maps at both SoC and IP -levels

- Additionally, in test chips it's common to use a large number of CSRs

- Enabling features that you want to be able to turn on/off (chicken bits)

- Debug

- Test purposes

- Generating and maintaining CSRs involves a large number of files:

- Multiple RTL files

- Documentation

- Programming model and views

- Test cases

- For agile research test chips, very helpful to avoid doing this by hand!

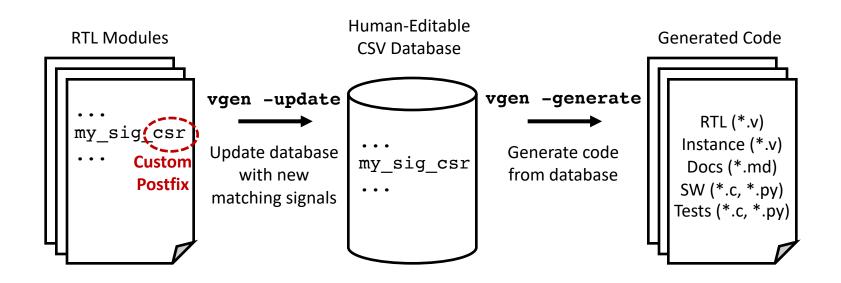

- CHIPKIT provides a simple flow to automatically generate CSRs from a single database using a VGEN Python script

- Register definition described in comma separated value (CSV) format

- Can be manually or automatically generated and updated

- Signal naming pre/post fix convention to identify registers in RTL

- Very lightweight to update and maintain

- Automatically generates everything required

- RTL, documentation, tests and software definitions in both C and Python

- Register definition described in comma separated value (CSV) format

- Other open source alternatives for auto generating CSRs

- Vregs https://www.veripool.org/wiki/vregs

- csrGen http://asics.chuckbenz.com/csrGenUsersManual.pdf

## Control and Status Registers (CSRs)

CSRs in CSV database – populate by hand or self-populate (and update as things change) from RTL module(s)

| Q5 $\stackrel{\blacktriangle}{\checkmark}$ $\times$ $\checkmark$ $f_X$ |                              |     |       |       |        |      |           |           |          |

|------------------------------------------------------------------------|------------------------------|-----|-------|-------|--------|------|-----------|-----------|----------|

| 4                                                                      | A                            | В   | С     | D     | E      | F    | G         | н         | ı        |

| 1                                                                      | name                         | idx | nbits | start | access | test | rval      | desc      |          |

| 2                                                                      |                              |     |       |       |        |      |           |           |          |

| 3                                                                      | # Integration test registers |     |       |       |        |      |           |           |          |

| 4                                                                      | dc_dummy0                    | 0   | 32    | 0     | rw     | 0    | 0x0000000 | Dummy 32b | register |

| 5                                                                      | dc_dummy1                    | 1   | 32    | 0     | rw     | 0    | 0x0000000 | Dummy 32b | register |

| 6                                                                      | dc_dummy2                    | 2   | 32    | 0     | rw     | 0    | 0x0000000 | Dummy 32b | register |

| 7                                                                      | dc_dummy3                    | 3   | 32    | 0     | rw     | 0    | 0x0000000 | Dummy 32b | register |

| 8                                                                      |                              |     |       |       |        |      |           |           |          |

| 9                                                                      | # NIC                        |     |       |       |        |      |           |           |          |

```

./vgen_regs.py --update ../CRG.sv --csv cregs.csv --prefix dc_

```

VGEN script reads the CSV database and automatically generates an RTL module for the registers and an instantiation template...

```

./vgen_regs.py --generate cregs.csv --clock HCLK --reset HRESETn --output output

```

```

module

// VGEN: MODULE NAME

cregs

// clocks and resets

input logic

clk,

input logic

rstn,

// Synchronous register interface

reg_intf.sink regbus,

// VGEN: OUTPUTS FROM REGS

output logic [31:0] dc_dummy0

/* idx #0: Dummy 32b register */

/* idx #1: Dummy 32b register */,

output logic [31:0] dc_dummy1

/* idx #2: Dummy 32b register */

output logic [31:0] dc_dummy2

/* idx #3: Dummy 32b register */,

output logic [31:0] dc_dummy3

output logic [0:0] dc nic dco en /* idx #4: */

```

```

logic [0:0] dc_dap_jtagtop;

logic [0:0] dc_dap_dbgswenable;

logic [0:0] dc_dap_deviceen;

logic [0:0] dc_eflx_pwr_on_en;

cregs u_cregs (

// clocks and resets

.clk(HCLK),

.rstn(HRESETn),

// Synchronous register interface

.regbus

(cregs.sink),

// reg file signals

.dc_dummy0(dc_dummy0[31:0]) /* idx 0 */,

.dc_dummy1(dc_dummy1[31:0]) /* idx 1 */,

.dc_dummy2(dc_dummy2[31:0]) /* idx 2 */,

.dc_dummy3(dc_dummy3[31:0]) /* idx 3 */,

.dc_nic_dco_en(dc_nic_dco_en[0:0]) /* idx 4 */

```

Automatically generates software views, e.g. Python class or C header

```

class Cregs(object):

def __init__(self,base_offset):

self.base_offset = base_offset

self.DC_DUMMY0 = self.base_offset + 0x0  # Dummy 32b register

self.DC_DUMMY1 = self.base_offset + 0x4  # Dummy 32b register

self.DC_DUMMY2 = self.base_offset + 0x8  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dummy 32b register

self.DC_DUMMY3 = self.base_offset + 0xc  # Dum

```

Automatically generates tests in C or Python

Automatically generates documentation in Markdown

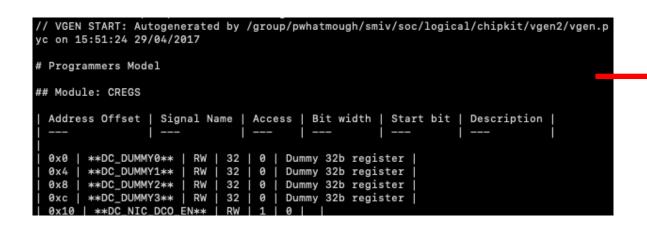

// VGEN START: Autogenerated by /group/pwhatmough/smiv/soc/logical/chipkit/vgen2/vgen.pyc on 15:51:24 29/04/2017

#### **Programmers Model**

#### **Module: CREGS**

| Address Offset | Signal Name   | Access | Bit width | Start bit | Description        |

|----------------|---------------|--------|-----------|-----------|--------------------|

| oxo            | DC_DUMMYo     | RW     | 32        | o         | Dummy 32b register |

| 0x4            | DC_DUMMY1     | RW     | 32        | o         | Dummy 32b register |

| ox8            | DC_DUMMY2     | RW     | 32        | 0         | Dummy 32b register |

| oxc            | DC_DUMMY3     | RW     | 32        | 0         | Dummy 32b register |

| 0x10           | DC_NIC_DCO_EN | RW     | 1         | o         |                    |

Clocks

Resets

Power Domains

#### Clocks

- Demands careful design, documentation and RTL hygiene

- Keep as simple as possible and document very clearly!

- Ideally, every block only has a single clock and reset and does not span clock domains by design

- Low-frequency clocks can be supplied from the PCB through the package

- Limited by the PCB/packaging parasitics and IO cell slew limitations typically works okay up to about 100MHz or so

- Typically also want faster clocks, especially in deep-nm technologies

- Do not generate clocks inside the IP, deliver from the SoC for better control / visibility / debug

- Internally-generated clocks

- Fixed-ratio of the bus or system clock

- Possible to use avoid async bridge for data moving between clock domains

- But, will need a more careful implementation of clock tree and timing closure

- Asynchronous requires a full asynchronous bridge CDC

- Caution: Dragons be here!! If you must do this, use pre-verified code and be careful

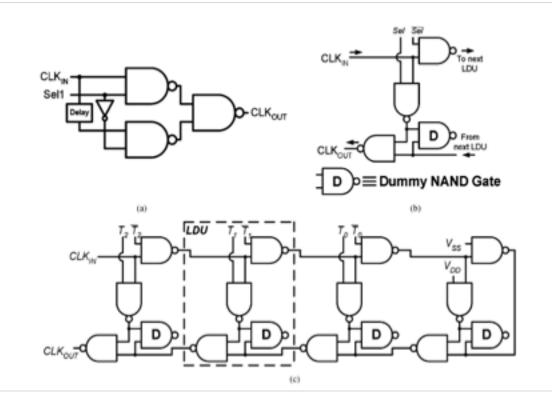

## CHPIKIT On-chip clock generation

- Standard IO cells do not work well above ~100MHz or so

- On-chip clock generation for faster clocks

- PLLs and related synthesizers

- Very low noise and drift

- High quality reference clock

- Dedicated clean decoupled power supply

- Careful layout integration

- Availability and cost

- Digitally-tuned open-loop oscillator

- Cheap and straightforward, no hand layout or analog macros

- Sufficient noise performance for high-performance digital

- Dedicated clean decoupled power rail

- All-digital implementation!

- Verilog netlist of standard cell instantiations

- Verify and tune using SPICE simulation

- Place and route automatically, or using constraints/directives

"A 40–550 MHz Harmonic-Free All-Digital Delay-Locked Loop Using a Variable SAR Algorithm", R-J Yang et al., JSSC'07

#### Resets

- Conceptually straightforward, but can easily cause catastrophic issues

- Keep as simple as possible and document very clearly!

- Stick to asynchronous active-low resets

- This uses the async reset pin on standard library flip-flops

- Don't get hung up on this, it's just a convention ©

- Only one reset per IP block clock domain

- in which case, use one reset per clock

- Ensure that reset generation is not done inside IP do at SoC level instead

- Do not use reset synchronizers when crossing clock domains

- Use the clock-off strategy instead

#### Power Domains

- Many reasons to have multiple power domains in your research test chips

- Functional e.g. IO cells and analog macros typically need various voltages

- Performance e.g. per-cluster or per-core voltage scaling, or clean PLL rails

- Measurement split out power consumption of different components (e.g. RAM vs logic power, or cache vs core power)

- But, power domains add a huge amount of complexity in both RTL and (especially) implementation, and a lot of risk!

- For research test chips, we suggest using a lightweight approach

- Multiple rails where necessary to achieve your research goals

- Try and avoid power gates and level-shifters, which add a huge amount of EDA complexity and risk

- Be careful with package design and pin allocation to ensure that power integrity is sufficient

# SoC RTL Validation

#### Front-End Validation Environment

- Setup a Makefile for front-end validation to make it easy to run single validation tasks or longer regressions

- Lint commercial tools, simple checkers

- Multiple synthesis tool front-ends

- Simulation regressions, RTL, synth/layout netlist +notiming, netlist SDF corners

- Logical equivalence checking (LEC)

- Formal verification

- Power-optimization tools clock gates and RAM enables

- Compiled simulators VCS/Verilator for fast regressions, possibly modelsim etc for interactive debugging

- Don't underestimate compute and disk space requirements, especially for regressions

- Escalates quickly for netlist sims and especially with timing annotation (will need runtime optimization...)

- Keep back-end stuff in a separate Makefile flow

- Front-end design will mainly use Synthesis, power analysis, timing analysis, etc

### SoC Test Coverage

- Basic tests

- Clock / reset / power stress tests

- Off-chip communication stress tests

- Per-block exercise test

- Transactions to cover all regs and mems

- Can be slow in some cases optimize for good coverage

- Ideally write/readback assuming R/W location in memmap

- Basic functionality tests, ideally fairly fast

- Whole memory map test

- Transactions to cover everything on the memory map

- Test unmapped regions too!

- Targeted application tests

- Ideally every test you want to measure on the silicon when it comes back

## M-Class SoC: Summary

- Keep things as simple as possible

- Essential to balance feature creep against risk and time

- Timing closure will be easier with good hierarchy choices

- And general hygiene e.g. hard timing boundaries inside block IO

- Invest in scripting for repetitive tasks

- Much easier to make changes and maintain

- Better reuse between projects

- Setup whole SoC as early as possible and build up incrementally

- Use integration shells for any new IP that does not yet exist

- Same for back-end implementation

#### Tutorial on Agile Research Test Chips Part 3: A-Class SoC

Paul Whatmough Marco Donato Glenn G. Ko Sae-Kyu Lee David Brooks Gu-Yeon Wei

School of Engineering and Applied Sciences

Harvard University

## M-Class SoC architecture example

#### Outline

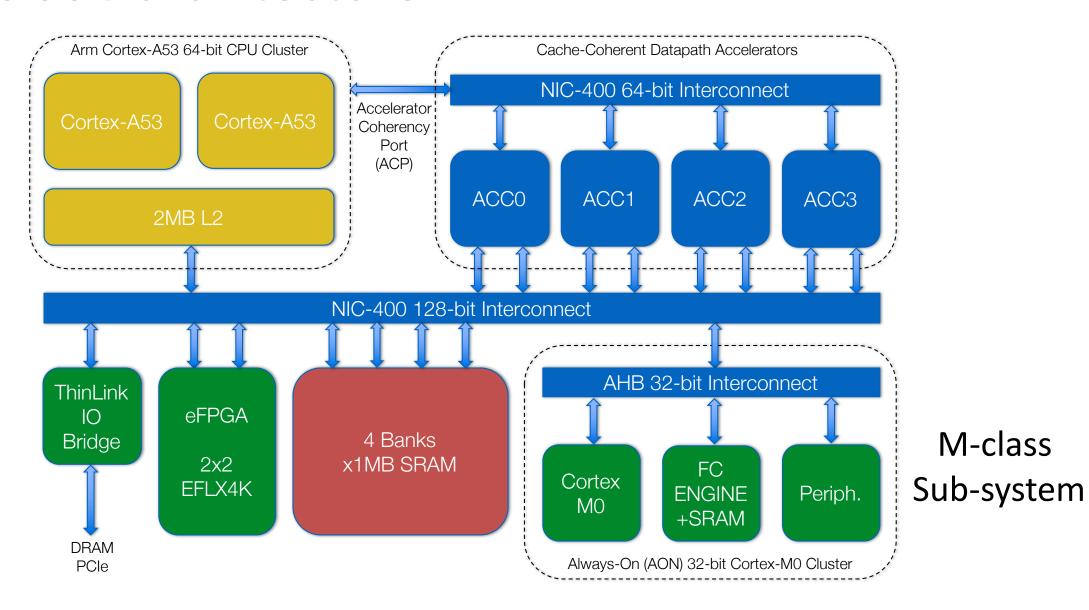

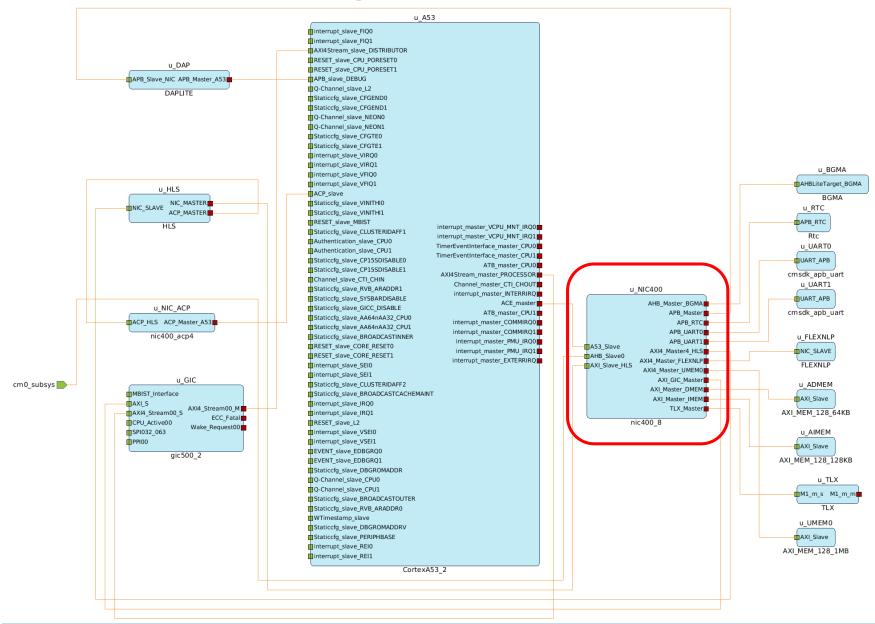

- SMIV A-Class SoC architecture

- Interconnect fabric

- NIC400 and AXI interfaces

- TLX400

- Socrates IP tooling flow

- Import IPs from arm IP catalog

- Configure and build a NIC400 interconnect

- Generate Verilog RTL

#### A-Class SoC architecture

# Interconnect fabric

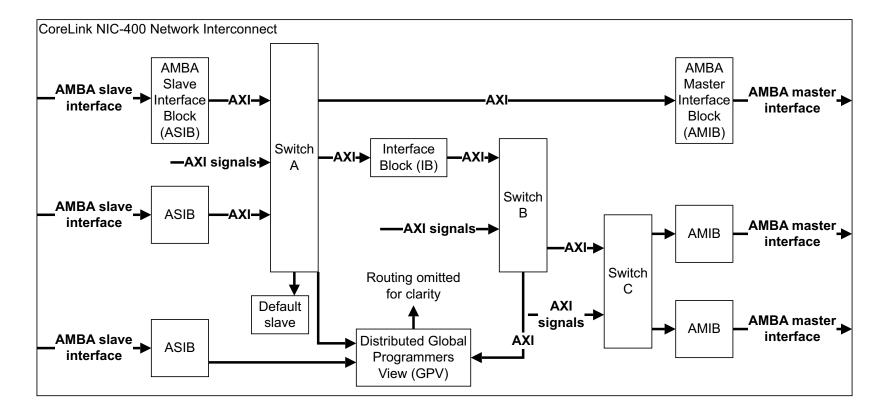

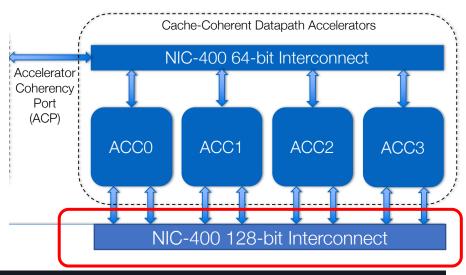

#### NIC400 interconnect

- Flexible interconnect that can host up to 128 master and 64 slave AMBA interfaces

- AMIBs and ASIBs provide AMBA master/slave interfaces

- IBs provide domain crossing and buffering functions

#### AXI interface

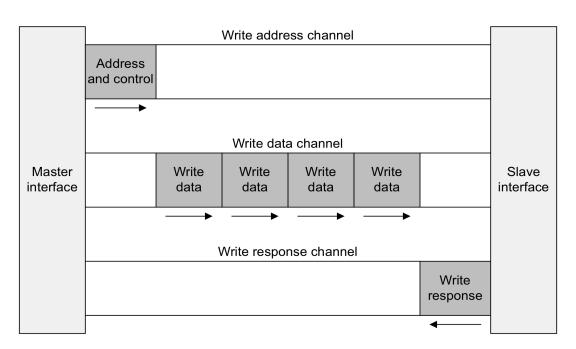

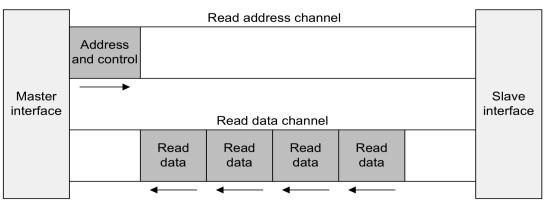

- AMBA AXI interface for high-throughput, low-latency

- Flexible

- Backward compatible with AHB and APB

- Interface uses 5 independent channels

- 2 address channels (read/write)

- 2 data channels (read/write)

- 1 response channel (write)

- Allows to operate with separate address/control data phases

- Supports unaligned data transfers using byte strobes

- Burst-transactions (fixed, incremented, or wrapped)

## AXI handshaking

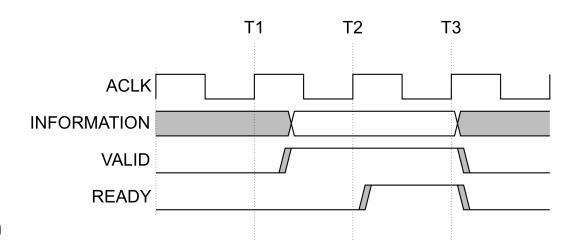

- AXI uses global clock and reset signals (ACLK and ARESETn)

- Each of the 5 channels uses VALID/READY signals to implement the same handshaking protocol

- The source generates the VALID signal when the information is available

- The sink generates the READY signal when it can accept the information

- The transaction takes place when both VALID and READY are high

- Both read and write data channels include a LAST signal which is asserted when the last transfer in a burst transaction is being driven

#### **AXI** variations

AXI-Lite targets simpler control register-style interfaces that might not need full AXI functionality

- Burst length fixed to 1

- Supports a data bus width of 32-bit or 64-bit

| Global  | Write address<br>channel | Write data<br>channel | Write response channel | Read address<br>channel | Read data<br>channel |

|---------|--------------------------|-----------------------|------------------------|-------------------------|----------------------|

| ACLK    | AWVALID                  | WVALID                | BVALID                 | ARVALID                 | RVALID               |

| ARESETn | AWREADY                  | WREADY                | BREADY                 | ARREADY                 | RREADY               |

| _       | AWADDR                   | WDATA                 | BRESP                  | ARADDR                  | RDATA                |

| _       | AWPROT                   | WSTRB                 | _                      | ARPROT                  | RRESP                |

AXI4-Stream protocol is used as a standard interface to connect components that wish to exchange data

Used to implement the point-to-point connection for data transfer

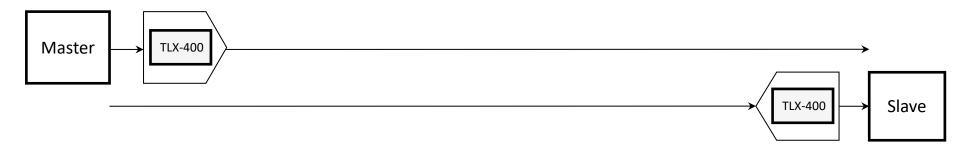

## TLX Bridge (ThinLink)

- Optional feature for the NIC400 interconnect

- Reduce number of signals compared to AXI

- Interconnect routed over a longer distance

- Supports only a single M/S interface to implement a forward and reverse link

- Supports clock domain crossing

- The physical layer is AXI-stream compliant

- Used for off-chip Wide I/O bridge to FPGA

- Access to additional IP (DRAM, PCIe, USB, etc.)

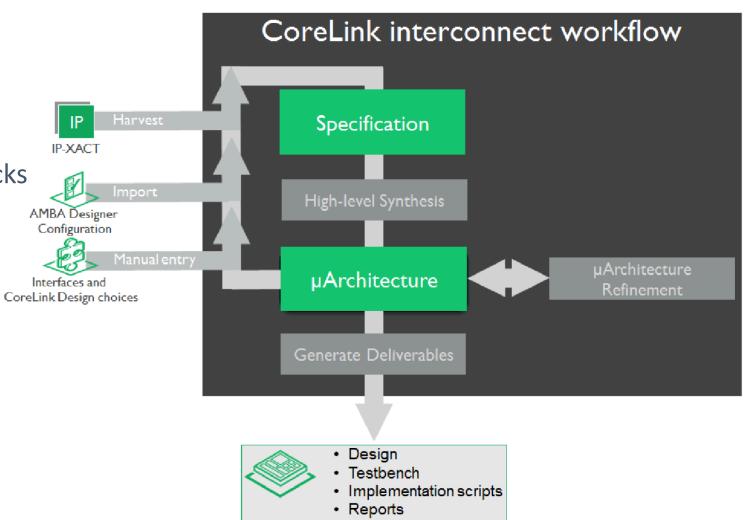

# Arm Socrates flow

## Arm Socrates IP tooling flow

- Arm IP configuration

- Cortex A53, system IPs

- External macro configuration

- Accelerators and custom blocks

- NIC400

- Clock domains definition

- Define interfaces

- Memory map

- Build

- RTL Verilog

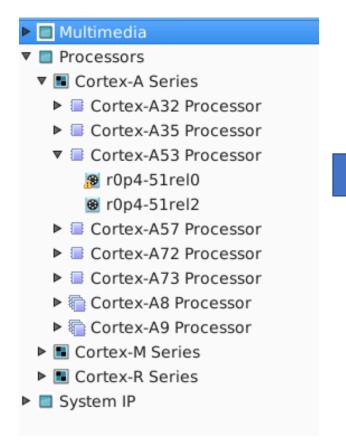

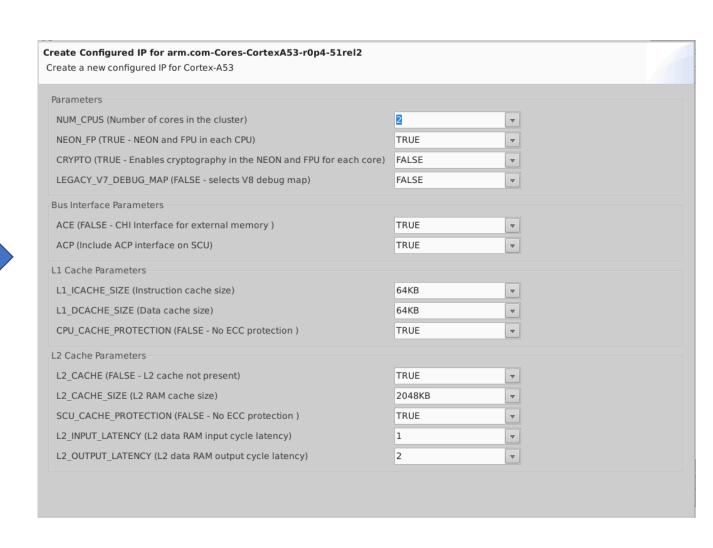

## Arm IP configuration - Cortex-A53

#### IP catalog offers a set of Arm IPs:

- Graphics and multimedia cores (Mali)

- Cortex A-, M-, and R- cores

- System controllers

#### NIC400 clocks

#### Clock domain creation and clock relationships

```

# Clock domains

createClockDomain(deCC, :name => "clk1", :frequency => "100", :powerdomainref => "pd0")

createClockDomain(deCC, :name => "clk2", :frequency => "100", :powerdomainref => "pd0")

createClockDomain(deCC, :name => "clk3", :frequency => "100", :powerdomainref => "pd0")

# Clock relationships

createClockRelation(deCC, :clockref1 => "clk1", :clockref2 => "clk0", :relationship => "asynchronous")

createClockRelation(deCC, :clockref1 => "clk0", :clockref2 => "clk2", :relationship => "identical")

createClockRelation(deCC, :clockref1 => "clk0", :clockref2 => "clk3", :relationship => "synchronous", :synchronoustype => "1:n")

createClockRelation(deCC, :clockref1 => "clk2", :clockref2 => "clk3", :relationship => "synchronous", :synchronoustype => "m:1")

createClockRelation(deCC, :clockref1 => "clk0", :clockref2 => "clk3", :relationship => "synchronous", :synchronoustype => "m:n")

```

## NIC400 configuration

#### Define interfaces

```

intf = createMasterIF(deCC, :name => "AXI_Master_ACCO", :clockref => "clk3")

setProtocolAttributes(intf, :protocol => "AXI4MasterProtocol", :datawidth => 128, :addresswidth => 32,

:multiregion =>"false", :trustzonemaster => "secure", :idwidthreduction => "false",

:programmable => "true")

masters << "AXI4_Master4_ACCO"</pre>

intf = createSlaveIF(deCC, :name => "AXI_Slave_ACCO", :clockref => "clk3")

setProtocolAttributes(intf, :protocol => "AXI4SlaveProtocol", :datawidth => 128, :addresswidth => 32, :programmable => "true",

:vidwidth => "6", :trustzoneslave => "secure", :readacceptance => "1", :writeacceptance => "1",

:localgroupref => "axi_inputs")

createPath(deCC, :source => "AXI_Slave_ACCO", :targets => masters)

slaves << "AXI Slave ACCO"</pre>

```

### NIC400 memory map

- Each slave can have its own address map

- Address regions must not overlap

- Regions must be aligned to 4KB boundaries

- Undefined memory regions routed to internal default slave

| Марр | ed Blocks for sele | cted Memory Map             |                     |        |          |                     |  |

|------|--------------------|-----------------------------|---------------------|--------|----------|---------------------|--|

|      | Offset             | Offset Range Default Target |                     | Region |          | Resolved Target     |  |

|      |                    |                             |                     |        | -        |                     |  |

| 1    | 0x30000000         | 0x00100000                  | AXI4_Master_UMEM0   | •      | •        | AXI4_Master_UMEM0   |  |

| 2    | 0x32000000         | 0x00100000                  | AXI4_Master4_HLS    | •      | <b>*</b> | AXI4_Master4_HLS    |  |

| 3    | 0x33000000         | 0x05000000                  | AXI4_Master_FLEXNLP | •      | -        | AXI4_Master_FLEXNLP |  |

| 4    | 0x31000000         | 0x00100000                  | AHB_Master_BGMA     | •      | <b>-</b> | AHB_Master_BGMA     |  |

| 5    | 0x08000000         | 0x00020000                  | AXI_Master_IMEM     | •      | -        | AXI_Master_IMEM     |  |

| 6    | 0x0c000000         | 0x00010000                  | AXI_Master_DMEM     | •      | -        | AXI_Master_DMEM     |  |

| 7    | 0x40000000         | 0xc0000000                  | TLX_Master          | •      | -        | TLX_Master          |  |

| 8    | 0x2c000000         | 0x00100000                  | AXI_GIC_Master      | •      | -        | AXI_GIC_Master      |  |

| 9    | 0x2a020000         | 0x00010000                  | APB_Master          | •      | -        | APB_Master          |  |

| 10   | 0x2a030000         | 0x00002000                  | APB_RTC             | •      | <b>-</b> | APB_RTC             |  |

| 11   | 0x2a000000         | 0x00001000                  | APB_UART0           | -      | +        | APB_UART0           |  |

| 12   | 0x2a010000         | 0x00001000                  | APB_UART1           | •      | -        | APB_UART1           |  |

| 13   | 0x2b000000         | 0x00100000                  | GPV                 | -      | -        | GPV                 |  |

## NIC400 IP integration

#### Q&A session

CHIPKIT Tutorial (Part 3)

Sun. May 31, 2020

10:30 AM - 10:45 AM

# Tutorial on Agile Research Test Chips Custom IP Development

Paul Whatmough Marco Donato Glenn G. Ko Sae-Kyu Lee David Brooks Gu-Yeon Wei

School of Engineering and Applied Sciences

Harvard University

#### **CHIPKIT Materials**

#### **IEEE Micro paper**

- https://ieeexplore.ieee.org/document/9096507

- https://arxiv.org/abs/2001.04504

#### CHIPKIT: An agile, reusable open-source framework for rapid test chip development

Paul N. Whatmough<sup>1,2</sup>, Marco Donato<sup>1</sup>, Glenn G. Ko<sup>1</sup>, David Brooks<sup>1</sup>, and Gu-Yeon Wei<sup>1</sup>

<sup>1</sup>Harvard University <sup>2</sup>Arm Research

Abstract—The current trend for domain-specific architectures (DSAs) has led to renewed interest in research test chips to demonstrate new specialized hardware. Tape-outs also ofter huge pedagogical value garnered from real hands-on exposure to the whole system stack. However, successful tape-outs demand hard-earned experience, and the design process is time consuming and fraught with challenges. Therefore, custom chips have remained the preserve of a small number of research groups, typically focused on circuit design research. This paper describes the CHIPNT framework. We describe a reusable SOC subsystem which provides basic IO, an on-chip programmable host, memory and peripherals. This subsystem can be readily extended with new IP blocks to generate oustom test chips. We also present an agile RTL development flow, including a code generation tool called VGEN. Finally, we outline best practices for full-chip validation across the entire design cycle.

Index Terms-Agile design, design reuse, testing, open-source

#### 1 Introduction

3

D ESEARCH test chips are the ultimate demonstration of In the true value of novel computer architecture innovations. In addition, taping out test chips in a research or academic setting provides huge pedagogical value, offering real insight across the whole stack. Nonetheless, despite all the upsides, taping-out test chips remains very challenging, especially for the uninitiated. Custom chips are time consuming to design, fabricate and test, and often error prone potentially requiring expensive re-spins to fix problems. In this paper, we explore two key themes of agile and reusable design, to help reduce the barrier to entry for chip tape-outs. Emphasizing reuse greatly reduces development cost and at the same time minimizes the opportunity for silicon bugs and allows the designer to focus on differentiating features. While agile design seeks to follow a methodology where changes can be readily implemented late into the design cycle, without significant disruption or risk.

Fig. 1. Three recent chips [1], [2], [3] built using the CHPIKIT framework

[2], through to large multi-accelerator SoCs with Arm Cortex-A multi-core CPU clusters [3]. However, they all share the same basic framework, with the same SoC subsystem for system bring up, communication and control. Following this framework has allowed new tape-outs to be developed with very low-risk and high success rate. To be In

#### Open source Github project

https://github.com/whatmough/CHIPKIT

#### Outline

- Overview

- Interface and Control

- Hardware Description

- SystemVerilog Coding Guidelines

- Summary

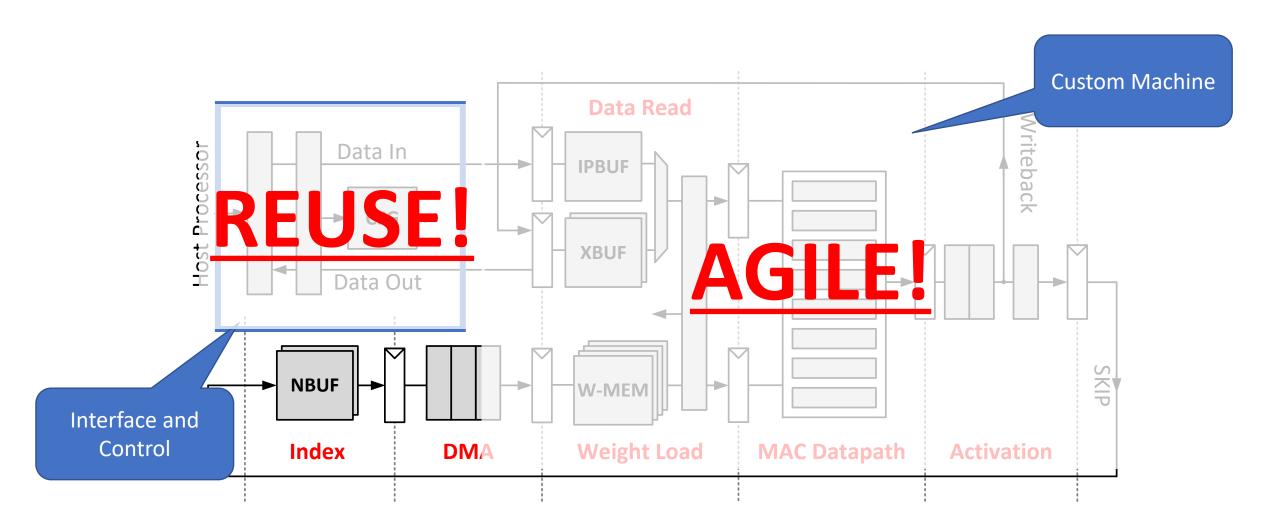

# Overview

The Interesting Bit!!

# Custom IP Development

# Interface and Control

#### Accelerator Interfaces

- Simple slave control "passive" accelerator programming model

- Configure accelerator for job

- Move data into internal RAM

- Start task and wait for a done signal (IRQ or poll register)

- Slave control with master for data (internal DMA)

- Configure accelerator for job

- Accelerator accesses data from provided addresses

- Run task and (optionally) move results to somewhere in memory

- Job queue control with master for data (internal DMA)

- Accelerator fetches job for queue in memory

- Accelerator accesses data from provided addresses

- Run task and (optionally) move results to somewhere in memory

#### Accelerator Interfaces

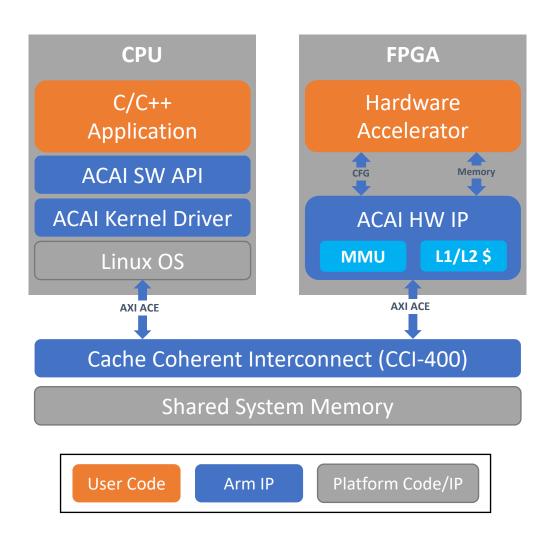

- Very active and arguably understudied aspect of modern SoCs

- Data movement cost

- Virtualization

- Coherency

- Arm A-Class cores feature Accelerator Coherency Port (ACP)

- Allows access directly into L2 cache of the CPU cluster

- Coherent to the CPU cache, without implementing dedicated coherency logic

- Arm Coherent Accelerator Interface (ACAI)

- Implements a coherent (ACE-lite) accelerator interface with RTL & SW

- All the benefit of coherency, without the complexity of implementing it!

### Arm Coherent Accelerator Interface (ACAI)

- Hardware and software framework to enable easy adoption of accelerators on SoC platforms

- Easier hardware accelerator integration

- ACAI provides accelerator with a coherent cache and virtual addressing capabilities

- Accelerator interfaces to ACAI using standard AXI protocol

- Compatible with Xilinx Vivado HLS (High-Level Synthesis)

- Simpler programming model

- Linux user application written in C/C++ runs on CPU easier to debug & modify

- ACAI software libraries and drivers assist with job creation, scheduling and dispatch

- Support for accelerator virtualization (sharing across different processes)

- Maximize performance gains and enable fine-grained task acceleration

#### Arm Coherent Accelerator Interface (ACAI)

#### Full System Coherence

- HW accelerator connected to ACAI HW IP

- User application written in C/C++ runs on CPU

- ACAI SW libraries assist with job creation, scheduling and dispatch

- ACAI kernel driver sets up application context, page tables and configures ACAI IP

- ACAI HW IP configures the accelerator, provides a coherent cache and memory interface

- User accelerator executes on user described job

#### Reduced accelerator dispatch time

- No explicit data copies

- No CPU flush/invalidate required

- Supports hardware pointer dereferencing

**FPGA Prototype Platform**

### Arm Coherent Accelerator Interface (ACAI)

Setup and dispatch an FFT job on ACAI framework

```

module ha fft (

input wire clk,

input wire reset n,

// Memory interface (AXI4 Master)

// ..

// Configuration interface (AXI4-Lite Slave)

// ..

input wire ai job start i,

output wire ai job complete o

reg [31:0] length;

reg [31:0] src addr;

reg [31:0] result addr;

// more code

endmodule // ha fft

```

```

void main() {

// initialize acai

acai *p_acai = new acai();

p_acai->init();

// setup job chain with a single job

vector<acaijd> job_chain;

job_chain.reserve(1);

// setup job descriptor to write 3 registers

job_chain.push_back(acaijd(3, 0));

job chain[0][0] = (uint32 t)length;

job_chain[0][1] = (uint32_t)src_data;

job_chain[0][2] = (uint32_t)result_data;

// start and wait on the job to complete

p_acai->start_job(job_chain[0]);

p_acai->wait_job(job_chain[0]);

// cpu reads results

// ..

};

```

### RTL IP Integration Shell

- Accelerator will need an internal memory map

- This is usually relative to whatever address it resides at the SoC-level

- Typically truncate address bits to the required internal address space

- Ensure RAMs and architectural registers are bus accessible for debug

- An RTL IP integration shell should be the first RTL task

- Effectively a bus functional model in synthesizable RTL

- This should be well thought out and documented

- Very useful for SoC designers and for back-end designers early on

- All inputs and outputs should be registered for easy timing closure

- The accelerator interfacing should ideally not change, even while the internal blocks are being developed

- Clear documentation

- A set of simple (SoC) tests will help ensure this

#### Control

- Simpler accelerators usually incorporate a control FSM

- Think carefully about the design of this, bugs may be difficult to work around

- Try and think through all the tests you need to do on silicon

- Various functional scenarios and use cases

- Debug scenarios visibility if when things go wrong

- Measuring performance

- cycle counters, memory accesses, instruction/operation counts

- Counter stop/start/clear conditions

- Measuring power

- Infinite loop mode, self-test mode

# RAMs and Control and Status Registers (CSRs)

- Make all RAMs bus accessible

- Really helps with debug, testing, margining etc

- CSRs are best scripted unless very minimal

- See previous example on the CSR VGEN script

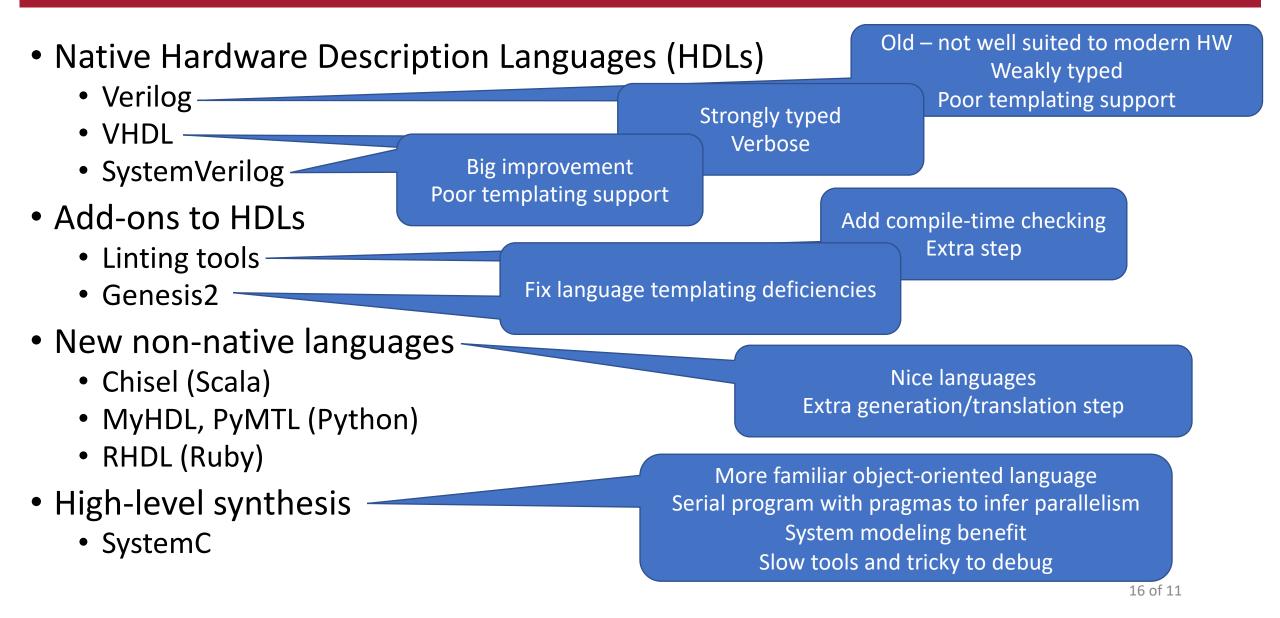

# Hardware Description

# Digital Hardware Design Methodologies

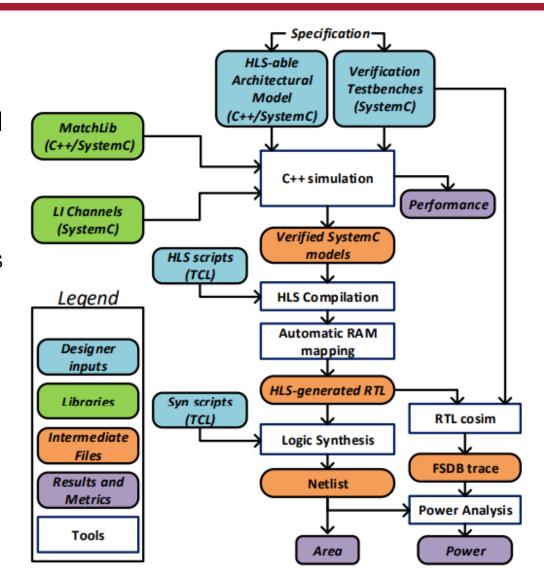

### Object-Oriented HLS Design Flow

- C++ to RTL to gates

- MatchLib: library of commonly-used macro-architectural components in HLS-able C++

- All communication between SystemC modules pass through Latency-Insensitive Channels and interconnects

- Reuse of C++/SystemC testbenches for simulation of HLS-generated RTL

- Productivity improvement over manual RTL coding and existing ad-hoc HLS-based flows

[Khailany et al., DAC'18]

# System Verilog Coding Guidelines

# Why SystemVerilog?

- We've had very fast results with HLS, potentially great for exploration

- For higher-performance designs, sometimes it's nice to have more control over pipelining

- We've used SystemVerilog extensively

- Native support in commercial EDA tools

- Much more compile time checking

- No translation step

- We've used a strict subset of SV for synthesizable code with good results

- Easy to learn

- Removes a large number of common bug classes

- Great PPA results

- Great correlation through front-end and back-end

- One drawback is less support for some features in open source simulators

#### Combinational Logic

- Separate combinational logic and sequential logic (flops)

- Extra compile time checking, easier pipeline adjustments, code readability

- Use logic type exclusively

- No need for the confusing wire/reg types

- Except for netlists use wire and use `default\_nettype none to catch undeclared nets that are usually typos

- Use lower-case signal names with underscores (\_)

- Except for top-level module port signals all caps by convention

- Use always\_comb keyword for all combinational logic

- Compile-time checking that latches or flops are not inferred (enforces above)

- Be careful with multiplexers

- Be careful with signed numbers in SV

### Combinational Logic

```

module my module (

// ...signals...

// Always split out logic and flops!

logic a, b, c; // Use logic type only

logic d, e, f; // Lower-case signals

always_comb a = b & c; // Single-line logic

always_comb begin  // multi-line logic

d = e \& f;

// more code

end

endmodule // my module

```

### Sequential Logic

- Separate combinational logic and sequential logic (flops)

- Extra compile time checking, easier pipeline adjustments, code readability

- Use the always\_ff keyword

- Compile-time checking that no flops are inferred in block (enforces above)

- Stick to positive-edge clocked, active-low asynchronous reset flops

- Use macro definition for inferring flops

- Enforces separation of logic and flops

- More compact, but still readable

- Easily swap out for different flops, e.g. synchronous reset for FPGA

- Use flop/RAM enable terms -> clock/RAM gating

### Sequential Logic

```

module my module (

// ...signals...

);

// Always split out logic and flops!

logic d_in, q_out; // Use logic type only

always_ff @(posedge clk, negedge rstn) begin

if(!rstn)

q out <= '0;

else

if(en)

q_out <= d_in;</pre>

end

endmodule // my module

```

```

`include RTL.svh

module my module (

// ...signals...

// Always split out logic and flops!

logic d_in, q_out; // Use logic type only

`FF(d_in, q_out, clk, en, rstn, '0);

endmodule // my_module

```

#### Module Declarations and Instantiations

- Use the SV syntax for module declarations

- Saves typing

- For module instantiation, use the automatic SV connections

- Use SV packages to group common functions and definitions

#### Module Declarations and Instantiations

```

module my module (

input logic clk,

input logic rstn,

// ...more signals...

// Module body

my_module2 u0 (

.clk,

// automatic connect

.rstn,

// ...more signals...

.signal99(),v // unused output

.signal100(other_sig) // override automatic

endmodule // my_module

```

#### **VGEN Scripts**

- SystemVerilog still has poor support for templating

- Generate statement and parameterization are both quite hard to use

- The perennial workaround for this is to write generators

- VGEN is a simple Python framework for writing generators quickly

- CSV database of objects, could be registers, pins, rams, pads, anything

- Implemented in Python as a list of dictionaries

- Tools to automatically populate and update this database from RTL, C,

Python, or even documentation

- Easy to use signal or module name pre/post -fix to mark things for automation

- Tools to generate RTL modules/instances, Python code, C code, Markdown, ...

# **VGEN Scripts**

### Module logging

- Opening waveforms should be a last resort during RTL development

- Simulation is slower

- Opening and working with a GUI is slow and clumsy

- Printing signals from a block-level test bench is quite clumsy

- Logging directly from an RTL module is a better approach

- Wrap non-synthesizable debug code in 'ifndef SYNTHESIS'

- Use reset signal to mask junk during reset

- Can generate a lot of clutter in the simulation transcript

- Even better is to log to file with module name

- You know where to look for module specific debug data

- Easy to parse in python to check against a model (especially datapath)

# Module Logging

```

module my module (

// ...signals...

// Module body

// Logging code

`LOGF_INIT // This macro opens the Log

`LOGF(clk, rstn, enable, format_expr)

`LOGF(clk, rstn,

iss.valid,

("| %s | %s |",iss.op,iss.data)

endmodule // my module

```

```

// Macro prototype

`LOGF(clk, rstn, enable, format_expr)

```

#### RAMs

- Think about physical design early on and for each node / library

- Understand the "best" RAM shapes/sizes in terms of PPA and features

- Use a generic RAM module interface to wrap actual instances with

- Makes changes much easier

- Wrap multiple smaller instances to make a big logical RAM

- Swap out RTL model, IP instantiation, FPGA inference template, etc.

- Recommend that IP-internal RAMs are memory mapped

- Makes bring up and test much easier

- Configuring margin adjustments

- Bus access timing paths can be made very slow if necessary, to aid timing closure

- Perform validation with RAM initial state of "X"

### Special cells

- "Architectural" clock gates are very common

- Different to inferred clock gates

- Useful to be able to turn off a whole block or turn off a whole clock domain etc

- Synchronization flip-flops

- Usually a double or triple back-to-back flop cell with some circuit optimizations

- Used for any async signals:

- clock domain crossing signals

- Input pins

- Async interrupts

- Reset synchronizers (but, don't use these!)

- For all these things, use a simple wrapped model for development, and be sure to swap this for a wrapped version of the library cell at implementation time

- Same as for RAMs

#### Front-End Validation

- RTL integration shell + tests

- Block level design

- Unit tests

- Linting

- LINK TO SV UNIT LEVEL TESTING

- Block integration tests

- Feature complete

- Clock gate / RAM enable optimization

- SoC integration tests

- Synthesis trials

- Timing analysis -> timing closure

- Power analysis -> power closure

- RTL freeze

#### Summary - Custom IP Development

- Think about IP interfacing carefully

- Use an IP integration shell to define connectivity early on

- Think about the usage model of the IP

- SystemVerilog subset for synthesis

- Front-end validation

# Tutorial on Agile Research Test Chips: Physical Design

Paul Whatmough Marco Donato Glenn G. Ko Sae-Kyu Lee David Brooks Gu-Yeon Wei

School of Engineering and Applied Sciences

Harvard University

#### **EDA Tools Overview**

- Design capture tools

- netlist entry, schematic, HDL, state diagram entry

- Simulation and verification tools

- functional (logic) sim and timing sim

- Synthesis and optimization tools

- creating netlists and optimizing them for timing and power

- Layout tools

- floorplanning, CTS, routing

#### Compute Platform Roadmap

#### **Synopsys Compute Platform Roadmap**

| Foundation | ROs Linux O/S Versions |                                                  | Windows<br>Platform                         |  |

|------------|------------------------|--------------------------------------------------|---------------------------------------------|--|

| R          | 2020.09                | RHEL 6.6+, 7.x, 8+                               | Windows                                     |  |

|            | 2020.12                | CentOS 6.6+, 7.1.1503+, 8+                       | 7, 10<br>Windows                            |  |

|            | 2021.03                | SLES 12+, 15+                                    | Server 2016                                 |  |

| Q          | 2019.12                |                                                  | Windows                                     |  |

|            | 2020.03                | RHEL 6.6+, 7.x, 8+<br>CentOS 6.6+, 7.1.1503+, 8+ | 7, 10<br>Windows                            |  |

|            | 2020.06                | SLES 12+, 15+                                    | Server 2008 R2,<br>2016                     |  |

| P          | 2019.09                | RHEL 6.6+, 7.x                                   | Windows 7, 10<br>Windows<br>Server 2008 R2, |  |

|            | 2019.06                | CentOS 6.6+, 7.x                                 |                                             |  |

|            | 2019.03                | SLES 11.4+ and 12.x                              | 2016                                        |  |

| 0          | 2018.12                | RHEL 6.6+, 7.x                                   | Windows 7, 10<br>Windows                    |  |

|            | 2018.09                | CentOS 6.6+, 7.x                                 | Server 2008 R2,<br>2016                     |  |

|            | 2018.06                | SLES 11.4 and 12.x                               |                                             |  |

| N          | 2018.03                |                                                  |                                             |  |

|            | 2017.12                | RHEL 6.6+, 7.x<br>SLES 11.x and 12.x             | Windows 7, 8,<br>10                         |  |

|            | 2017.09                |                                                  |                                             |  |

| М          | 2017.06                |                                                  |                                             |  |

|            | 2017.03                | RHEL 6.6+, 7.x<br>SLES 11.x and 12.x             | Windows 7, 8,<br>10                         |  |

|            | 2016.12                |                                                  |                                             |  |

Starting 2019.03 CentOS becomes the "build" platform and RHEL will be supported as a "binary compatible" OS

#### 2019-2021 Cadence Compute Platform Roadmap

|              | •          |                   |      |              |      |

|--------------|------------|-------------------|------|--------------|------|

| Arch         | OS<br>Name | OS<br>Version     | 2019 | 2020         | 2021 |

| x86_64       | RHEL       | 6.5+              |      |              |      |

|              |            | 7                 |      |              |      |

|              |            | 8                 |      |              |      |

|              | SLES       | 11 SP4            |      |              |      |

|              |            | 12                |      |              |      |

|              | Ubuntu     | 14.04             |      |              |      |

|              | CentOS*    | 6.5+              |      |              |      |

|              |            | 7                 |      |              |      |

|              |            | 8                 |      |              |      |

|              | Windows    | Win 7             |      |              |      |

|              |            | Win 10            |      |              |      |

|              |            | Server 2012       |      |              |      |

|              |            | Server 2016       |      |              |      |

| IBM<br>POWER | RHEL LE    | 7.2               |      |              |      |

|              |            | 8.1               |      |              |      |

| Arm v8       | RHEL       | 7.4+              |      |              |      |

|              |            | 8                 |      |              |      |

| Supported    |            | Selected products | 1    | lot supporte | d    |

Cadence supports CentOS but disclaims any liability for any errors or bugs in CentOS

#### Hierarchical Design

- vs. flat design

- better for complex chip design

- runtime is fast (run individual blocks)

- can fix timing issues on individual blocks

- · incremental functional and timing fixes

- Timing budgeting is required

- Floorplanning is important

- interconnects between blocks

- routing congestions

- I/O budgeting

- Signoff is usually done using a flat view

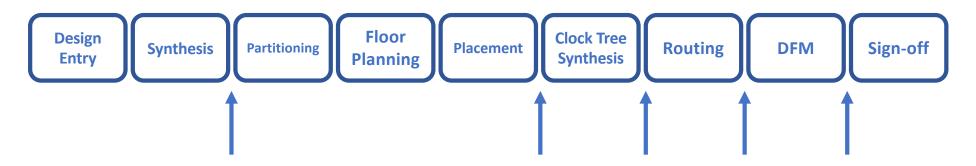

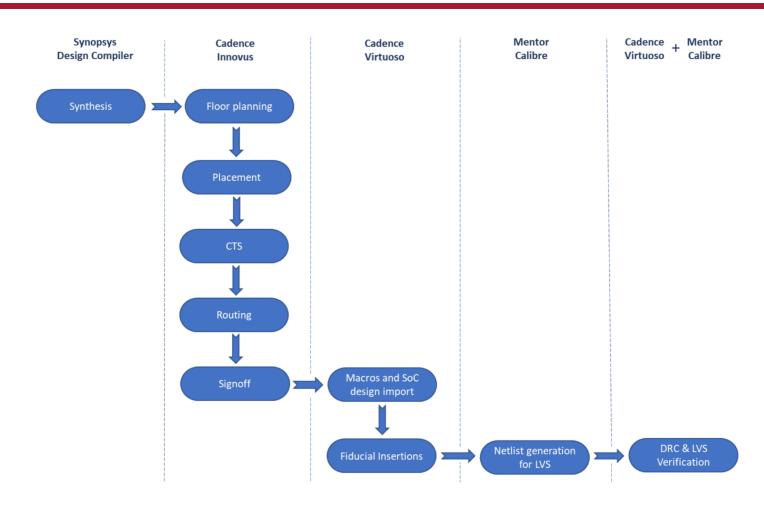

#### ASIC Design Flow

Design Entry

Synthesis

Partitioning

Floor Planning

Placement

Clock Tree Synthesis

Routing

DFM

Sign-off

#### Design Entry

- Input: RTL or System-C (other high-level language)

- Output: Verified RTL

- Functional simulation and testbench verification

- Tools: Synopsys VCS, Cadence Xcelium

- High-level Synthesis

- Tools: Synopsys Synphony C, Cadence Stratus, Mentor Catapult

- refer to Part 2: "Closing the algorithm/hardware design and verification loop with speed via high-level synthesis", Thierry Tambe (Harvard)

#### Synthesis

• Input: RTL, library files

• Output: Gate level netlist

- Synthesizes gate level netlist from RTL

- Reports area, power, timing estimations

- (DFT Insertion)

- Tools: Synopsys Design Compiler, Cadence Genus-RTL

#### Partitioning

- Partitioning involves dividing the logic into different logical groups and clock groups

- Synopsys IC Compiler II, Cadence Innovus

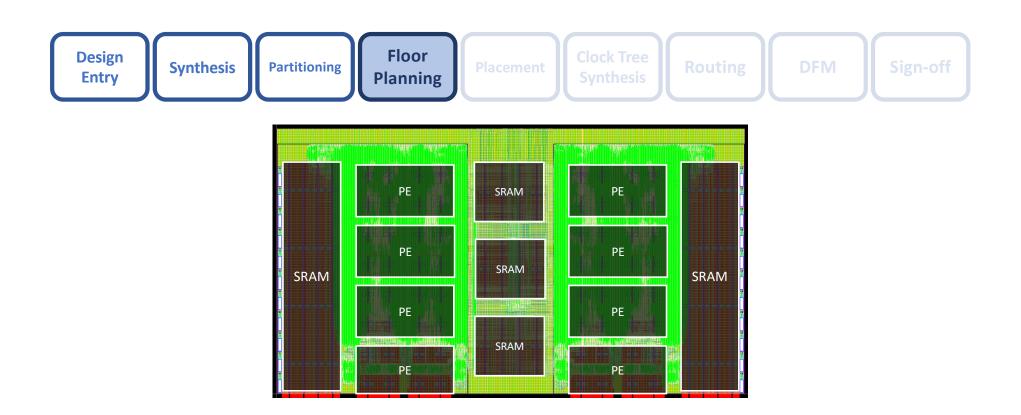

#### Top-level Floor Planning

- Inputs: synthesized netlist, view definitions (libraries, corners, constraints, etc.)

- I/O constraints: aspect ratio, I/O to core clearance, boundaries

- I/O pad, bump allocation

- Placement of macros and SRAMs, halos for them, I/O filler cells

- Synopsys IC Compiler II, Cadence Innovus

#### Block-level Floor Planning

- Inputs: synthesized netlist, view definitions (libraries, corners, constraints, etc.)

- I/O constraints: aspect ratio, I/O to core clearance, boundaries

- Place of SRAM cells, halos around SRAM, boundary cells and well traps

- Place Macro ports

- Synopsys IC Compiler II, Cadence Innovus

## Block-level Floor Planning Example

### Power planning

- Core power ring, macro power ring, metal straps, vias over VDD and VSS power structures

- Tools: Synopsys IC Compiler II (+PrimePower), Cadence Innovus

#### Placement

- Preplace, in-placement, post-placement optimization before CTS

- Synopsys IC Compiler II, Cadence Innovus

#### Clock Tree Synthesis

- Buffer sizing, relocation, fix hold, post placement optimization after CTS, clock gating

- Synopsys IC Compiler II, Cadence Innovus

#### Routing

- Timing and congestion driven, net constraints, global route, track assignments, detail route, search and repair, post route optimization, via and wire length optimization

- Synopsys IC Compiler II, Cadence Innovus

#### DFM

- Notch and metal filling, filler cell insertion, fiducial insertion

- Synopsys IC Compiler II, Cadence Innovus, Cadence Virtuoso

#### Timing Analysis and SI Analysis

- Inputs: .SPEF file

- RC extraction

- Synopsys StarRC, Cadence Quantus

- Signoff static timing analysis using parasitics

- Synopsys PrimeTime, Cadence Tempus

#### **Functional Verification**

- Inputs: .SDF file

- SDF back-annotated functional simulation

- contains timing information from the layout

- Synopsys VCS, Cadence Xcelium,

#### Formal Verification

- Inputs: .v or .db netlist

- Formal equivalence verification

- Synopsys Formality, Cadence JasperGold

#### Physical Verification

- Inputs: GDS II

- Design rule checking (DRC) and Layout Versus Schematic (LVS)

- Mentor Calibre + Cadence Virtuoso (Or Synopsys IC Validator, Cadence Pegasus)

### Complete flow

May reiterate different parts of the flow as needed

#### Focus: Logic Design to Physical Design

- Write RTL

- 2. Do functional verification

- 3. Run synthesis with constraints

- 4. Check if results are satisfactory

- If not run go back to 3 or 1

- 5. Run functional and formal verification on the results

#### Functional, Timing, Formal Verifications

This is an example of when you where you may want to perform functional verification, STA and Eq. checking to make sure the timing requirement is met and that the resulting gate-level netlist is functionally equivalent to the original RTL

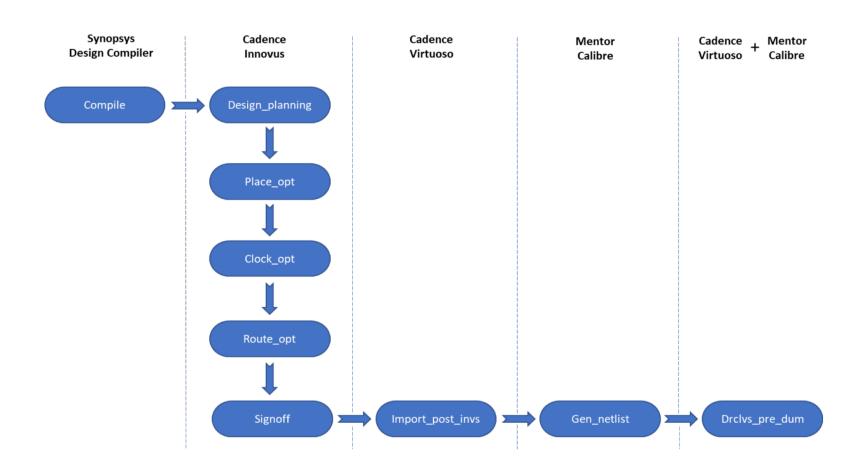

# Example: Block-level

# Example: Top-level

#### Tips

- Watch the disk space

- Sharing machine resources

- Use Skylake or newer machines for layout if possible

- More DRAM the better; 128GB+ or more

- Do DRC and LVS on initial design as soon as you can

- esp. if first time through the flow

- Do practice tape out to MOSIS well before the deadline

# Q&A Session

- CHIPKIT Tutorial (Part 5)

- Sun. May 31, 2020

- 11:00 AM 11:15 AM

# Tutorial on Agile Research Test Chips Part 6: Bring-up and Testing

Paul Whatmough Marco Donato Glenn G. Ko Sae-Kyu Lee David Brooks Gu-Yeon Wei

School of Engineering and Applied Sciences

Harvard University

#### Outline

- Test Board overview

- Connectivity

- Functional blocks

- Clot testing software

- Run programs on the SoC

- Voltage and Frequency scaling functions

- Measurement sweep template

# Test board overview

#### A-Class SoC architecture

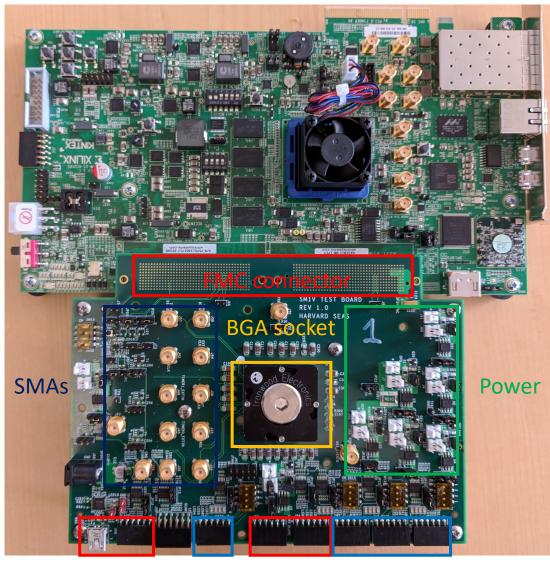

# Test board and FPGA setup

- DARPA CRAFT BGA flip chip socket

- Power supply connections

- USB to UART interface

- General Purpose IO for debugging

- SMA clock connections

- FPGA Mezzanine Card (FMC) connector

- Kintex KCU105

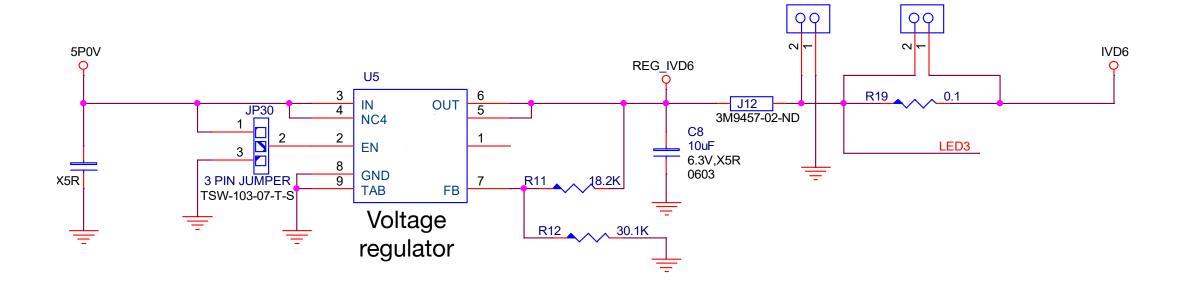

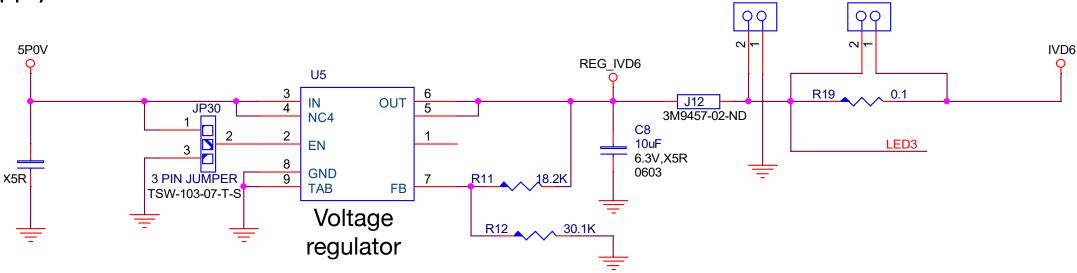

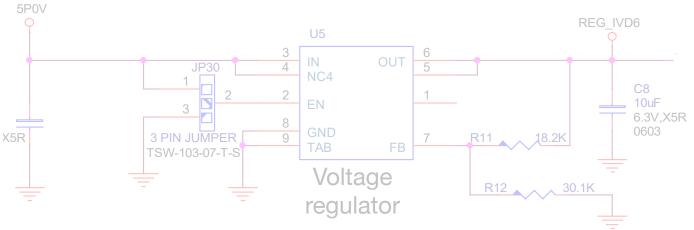

# Power Delivery – mode I

V<sub>DD</sub> is generated from a 5V switching power supply and an on-board voltage regulator

Useful for nominal operation and initial debugging

# Power Delivery – mode I with current read

V<sub>DD</sub> is generated from a 5V switching power supply and an on-board voltage regulator

Useful for nominal operation and initial debugging

Supply current can be measured with a DMM

**DMM**

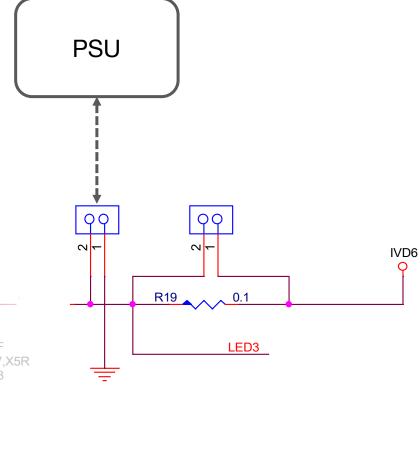

# Power Delivery – mode II

The power pin is decoupled from the on-board voltage regulator

V<sub>DD</sub> is generated from a programmable PSU

Required for running voltage scaling measurements

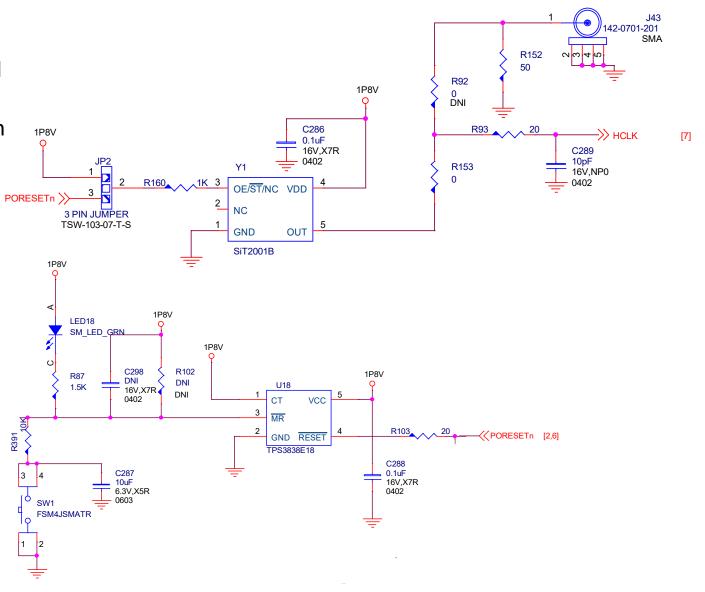

# Clocking and Resets

Single off-chip clock (HCLK)

HCLKis connected to the SoC input pin and a SMA connector for debugging

Faster clocks are generated on chip and can be routed internally to the DIAG block

The board is design with power-on reset capabilities

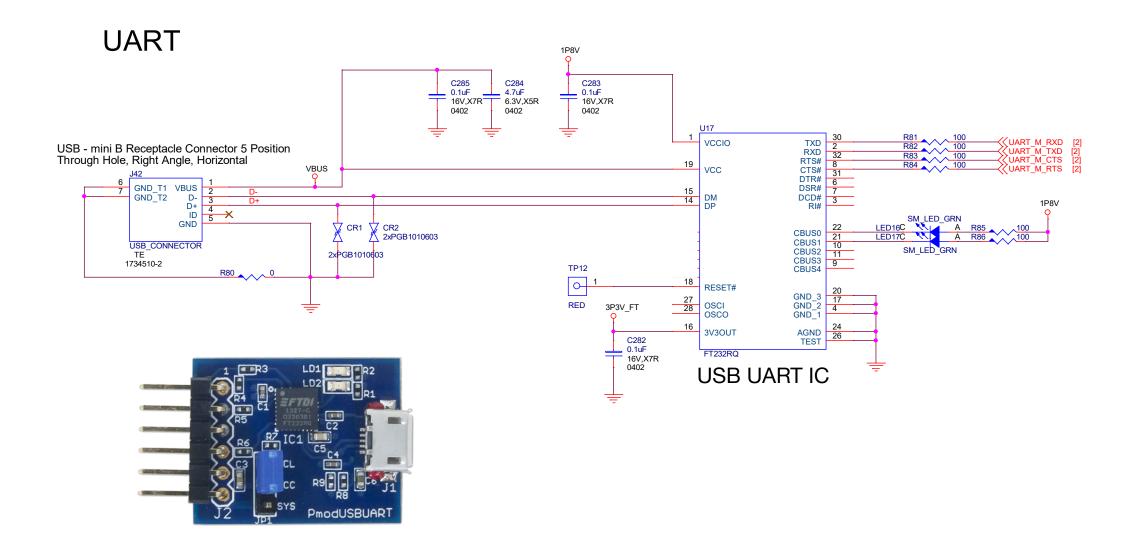

- The reset can be manually triggered via push-button

- During power-on, PORESETn is asserted when the supply voltage V<sub>DD</sub> becomes higher than 1.1 V and deasserted after a fixed delay time (200ms)

# USB interface

# Clot testing software

# CLOT – Chip LOad Tool

CLOT provides a set of python functions that allow to talk to the UART interface:

- Check the status of the slave interface

- Configure the DIAG mux for debugging internal signals

- Load hex files to a user-specified memory

- Dump memory content to a hex file

- Memory testing capabilities

- Configure internal CRG registers for clock and reset

- Run programs loaded in memory

Uses VISA API to interface with other instrumentation (PSU, Scope, DMM)

M0 load and run example:

clot -load imem hex/M0/hello.vhx -run

# CLOT – Load (1)

- Open hex file

- Read 32bit word

- Compute next address and write

```

def write_mem_hexfile(ser,base_addr,hex_file,size=None):

Keep writing until reach end of file or hit size bytes.

Each line in the hex file must either be "", start with "//",

or contain no more than 8 hex digits

# Open file

assert os.path.isfile(hex_file), 'File missing: %s' % hex_file

f_hex = open(hex_file, "r")

# Write to MEM line by line

i = 0

for line in f_hex:

if size != None and not i < (size / 4):</pre>

break

# Ignore comment lines etc

line = line.rstrip()

if line == "" or "//" in line:

continue

assert len(line) <= 8</pre>