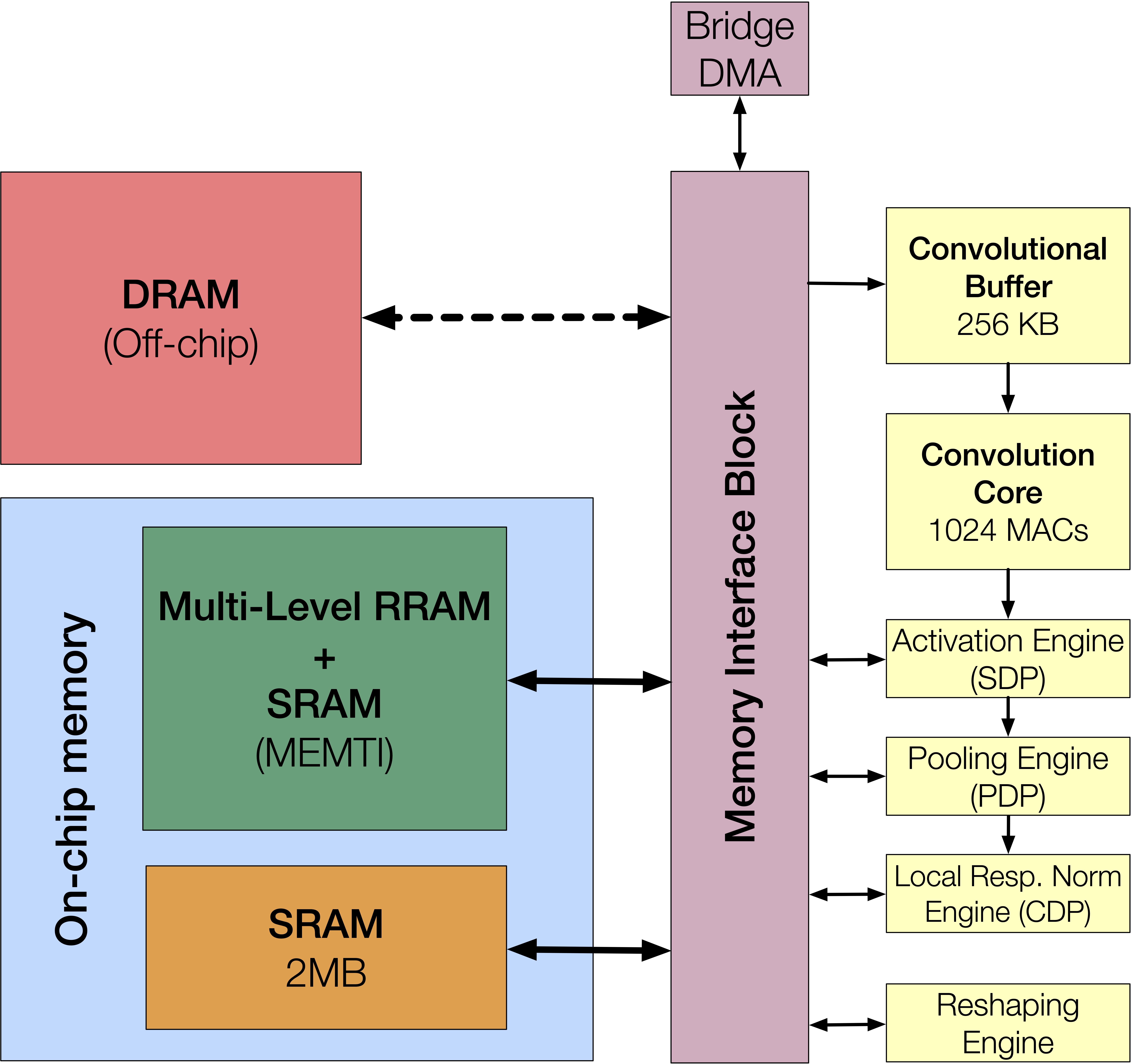

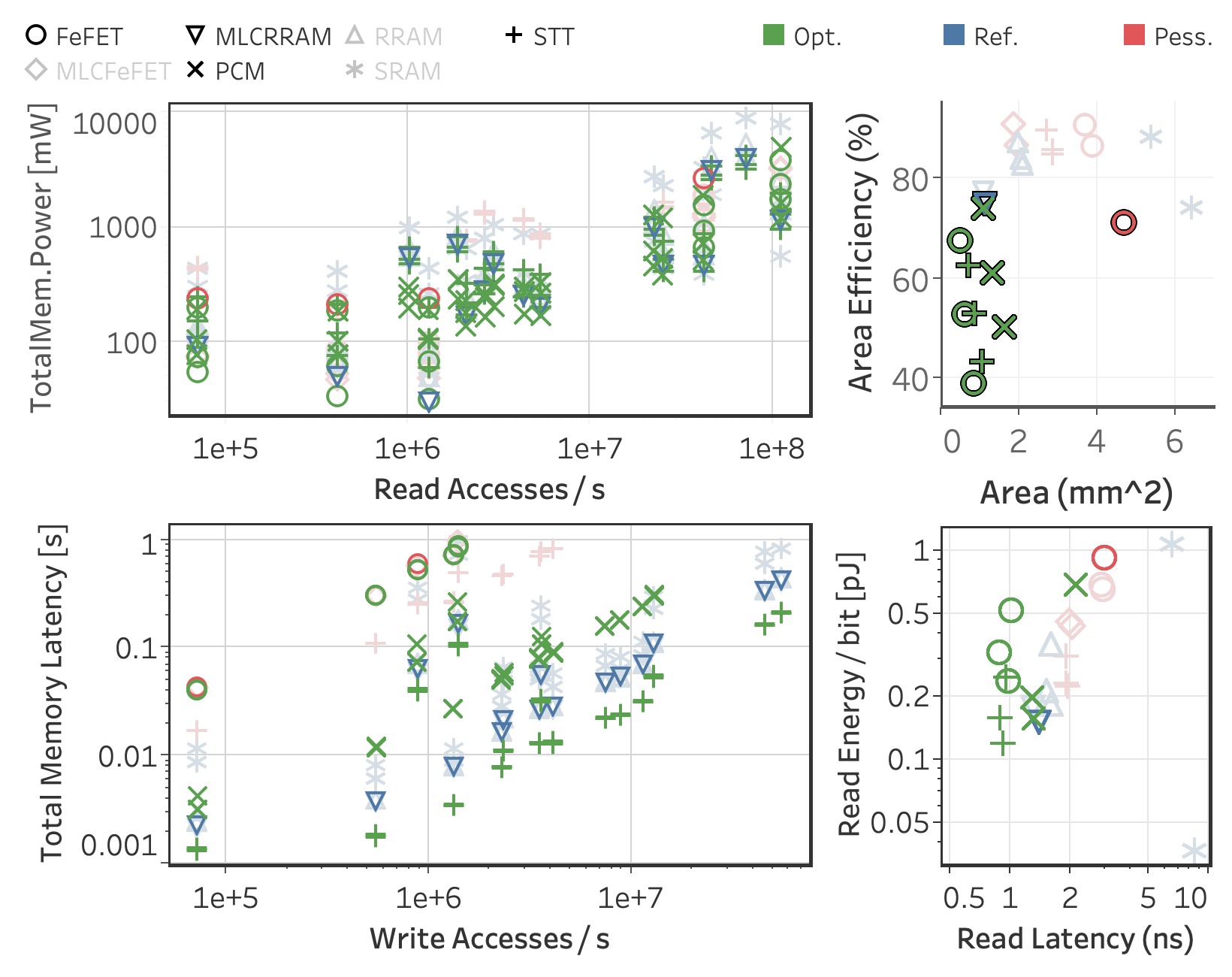

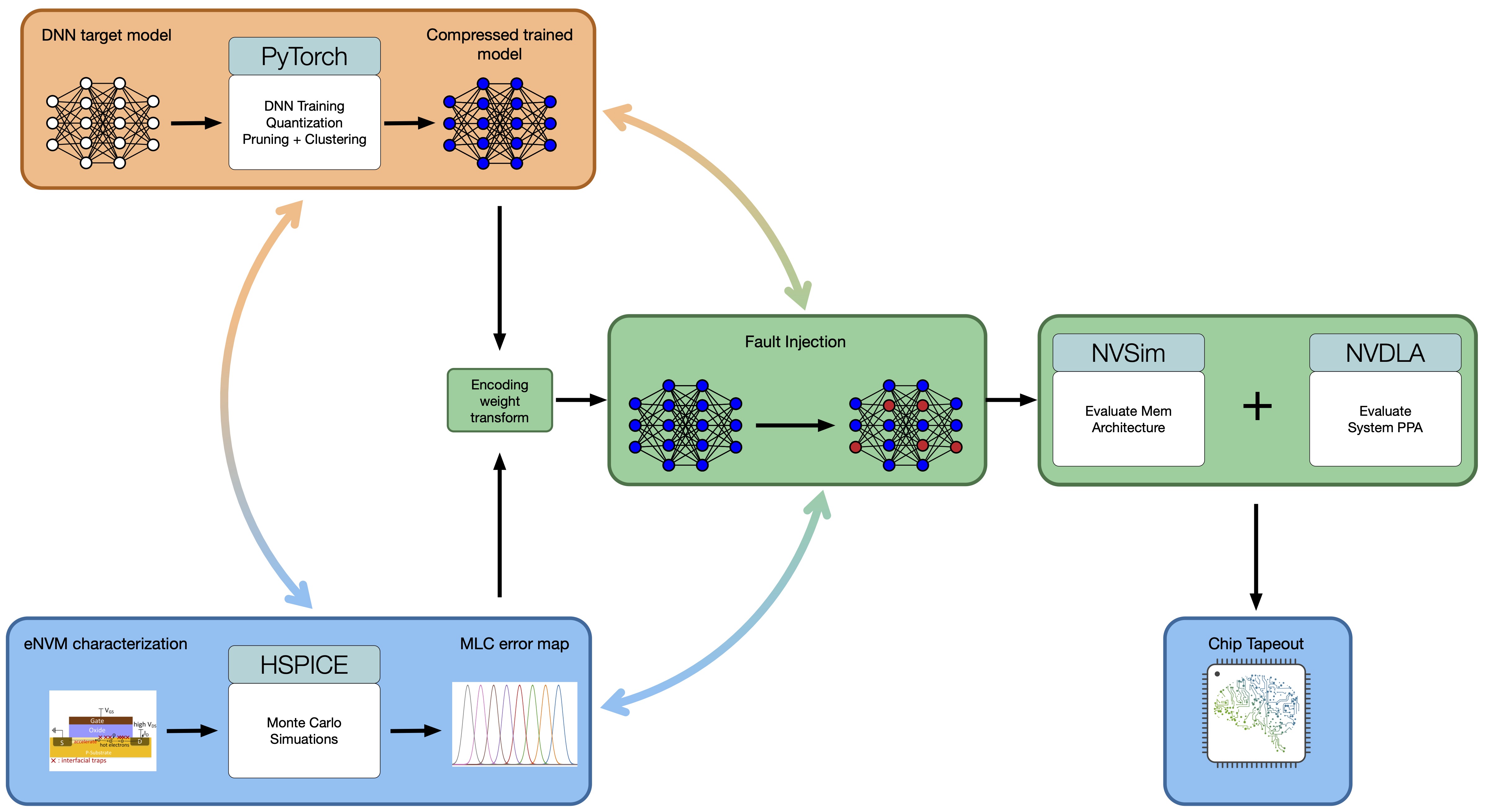

The “memory wall” problem has emerged as one of the main energy bottlenecks in many data-intensive applications (e.g. deep neural networks (DNNs) and graph processing). Emerging non-volatile memory technologies are a promising solution for implementing dense, energy-efficient on-chip memories. However, these new technologies are often limited by their programming performance and reliability. In this project, we investigate the interplay between NVM device characteristics, programming schemes, and memory array architectures to expose different design choices with the goal of optimizing performance, energy, area, and accuracy metrics for data-intensive workloads.